- 您现在的位置:买卖IC网 > PDF目录17109 > EVAL-ADUC7124QSPZ (Analog Devices Inc)BOARD EVALUATION FOR ADUC7124 PDF资料下载

参数资料

| 型号: | EVAL-ADUC7124QSPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 31/108页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR ADUC7124 |

| 设计资源: | EVAL-ADUC7124 Schematic ADUC7124 Eval Brd Gerber Files |

| 标准包装: | 1 |

| 系列: | MicroConverter® ADuC7xxx |

| 类型: | MCU |

| 适用于相关产品: | ADUC7124 |

| 所含物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

Data Sheet

ADuC7124/ADuC7126

Rev. C | Page 29 of 108

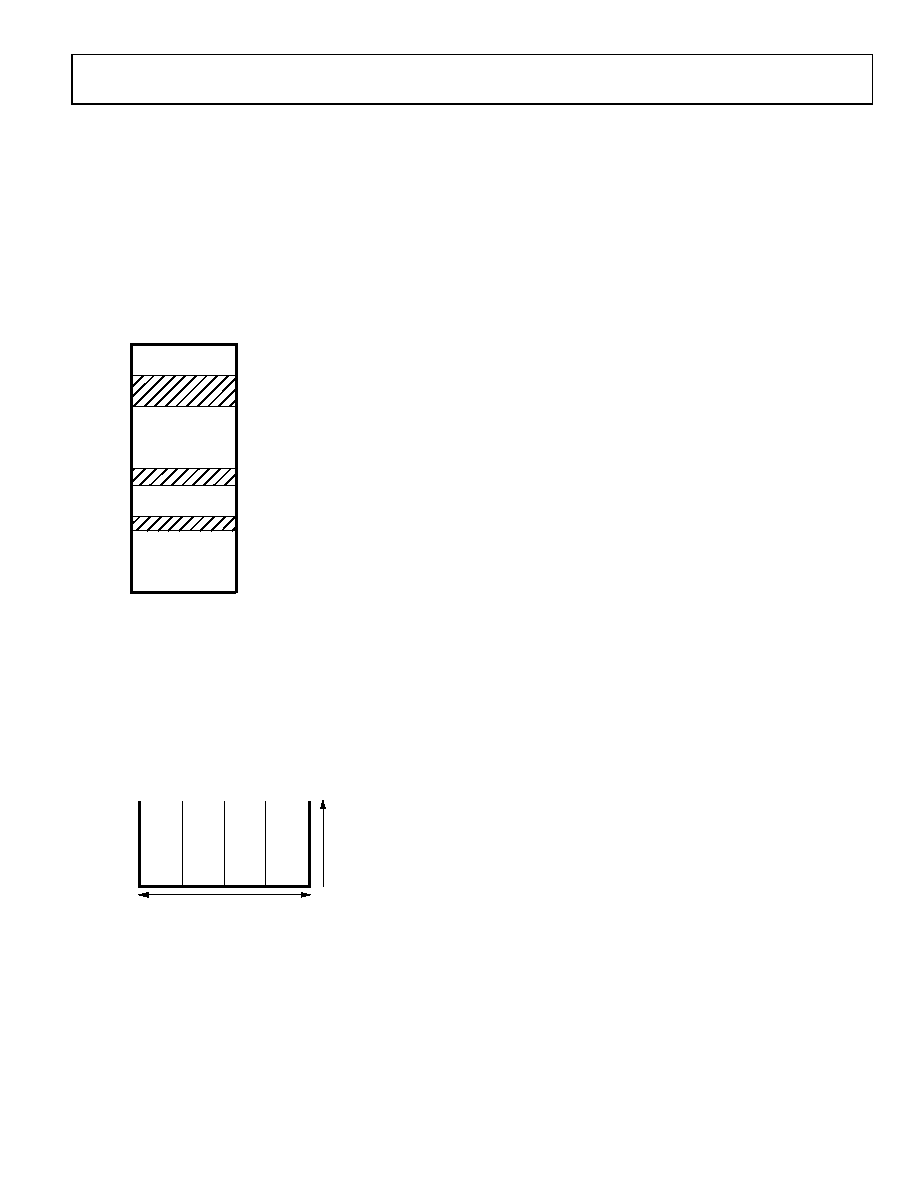

MEMORY ORGANIZATION

The ADuC7124/ADuC7126 incorporate three separate blocks

of memory: 32 kB of SRAM and two 64 kB blocks of on-chip

Flash/EE memory. There are 126 kB of on-chip Flash/EE memory

available to the user, and the remaining 2 kB are reserved for the

system kernel. These blocks are mapped as shown in Figure 24.

Note that, by default, after a reset, the Flash/EE memory is

mirrored at Address 0x00000000. It is possible to remap the

SRAM at Address 0x00000000 by clearing Bit 0 of the REMAP

MMR. This remap function is described in more detail in the

Flash/EE memory chapter.

RESERVED

0x00080000

FLASH/EE

RESERVED

0x00047FFF

0x00040000

SRAM

0xFFFF0000

0xFFFFFFFF

MMRs

0x0001FFFF

0x00000000

0x0009F800

RESERVED

REMAPPABLE MEMORY SPACE

(FLASH/EE OR SRAM)

09

12

3-

02

5

Figure 24. Physical Memory Map

MEMORY ACCESS

The ARM7 core sees memory as a linear array of a 232 byte

location where the different blocks of memory are mapped as

outlined in Figure 24.

The ADuC7124/ADuC7126 memory organization is configured

in little endian format: the least significant byte is located in the

lowest byte address and the most significant byte in the highest

byte address.

BIT 31

BYTE 2

A

6

2

.

BYTE 3

B

7

3

.

BYTE 1

9

5

1

.

BYTE 0

8

4

0

.

BIT 0

32 BITS

0xFFFFFFFF

0x00000004

0x00000000

09

12

3-

02

6

Figure 25. Little Endian Format

FLASH/EE MEMORY

The 128 kB of Flash/EE are organized as two banks of 32 kB ×

16 bits. In the first block, 31 kB × 16 bits is user space and 1 kB

× 16 bits is reserved for the factory-configured boot page. The

page size of this Flash/EE memory is 512 bytes.

The second 64 kB block is organized in a similar manner. It is

arranged in 32 kB × 16 bits. All of this is available as user space.

The 126 kB of Flash/EE are available to the user as code and

nonvolatile data memory. There is no distinction between data

and program because ARM code shares the same space. The

real width of the Flash/EE memory is 16 bits, meaning that, in

ARM mode (32-bit instruction), two accesses to the Flash/EE

are necessary for each instruction fetch. Therefore, it is recom-

mended that Thumb mode be used when executing from

Flash/EE memory for optimum access speed. The maximum

access speed for the Flash/EE memory is 41.78 MHz in Thumb

mode and 20.89 MHz in full ARM mode (see the Execution

Time from SRAM and Flash/EE section).

SRAM

The 32 kB of SRAM are available to the user, organized as

8 kB × 32 bits, that is, 16 kB words. ARM code can run directly

from SRAM at 41.78 MHz, given that the SRAM array is

configured as a 32-bit wide memory array (see the Execution

Time from SRAM and Flash/EE section).

MEMORY MAPPED REGISTERS

The memory mapped register (MMR) space is mapped into the

upper two pages of the memory array and accessed by indirect

addressing through the ARM7 banked registers.

The MMR space provides an interface between the CPU and

all on-chip peripherals. All registers except the core registers

reside in the MMR area. All shaded locations shown in Figure 26

are unoccupied or reserved locations and should not be

MMR memory map.

The access time reading or writing a MMR depends on the

advanced microcontroller bus architecture (AMBA) bus used

to access the peripheral. The processor has two AMBA buses:

the advanced high performance bus (AHB) used for system

modules, and the advanced peripheral bus (APB) used for the

lower performance peripheral. Access to the AHB is one cycle,

and access to the APB is two cycles. All peripherals on the

ADuC7124/ADuC7126 are on the APB except the Flash/EE

memory and the GPIOs.

相关PDF资料 |

PDF描述 |

|---|---|

| ECM30DCWN | CONN EDGECARD 60POS DIP .156 SLD |

| EVAL-ADUC7121QSPZ | BOARD EVALUATION FOR ADUC7121 |

| EVAL-ADUC7126QSPZ | BOARD EVALUATION FOR ADUC7126 |

| REC5-243.3SRWZ/H4/A | CONV DC/DC 5W 9-36VIN 3.3VOUT |

| EVAL-ADUC7023QSPZ | KIT DEV FOR ADUC7023 QUICK START |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC7126QSPZ | 功能描述:BOARD EVALUATION FOR ADUC7126 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:MicroConverter® ADuC7xxx 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EVAL-ADUC7128QSPZ | 功能描述:KIT DEV FOR ADUC7128 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:QuickStart™ PLUS 套件 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| EVAL-ADUC7128QSPZ2 | 制造商:AD 制造商全称:Analog Devices 功能描述:Precision Analog Microcontroller ARM7TDMI MCU with 12-Bit ADC and DDS DAC |

| EVAL-ADUC7129QSPZ | 制造商:Analog Devices 功能描述:- Bulk |

| EVAL-ADUC812QS | 制造商:Analog Devices 功能描述:DEVELOPMENT KIT SYSTEM |

发布紧急采购,3分钟左右您将得到回复。