- 您现在的位置:买卖IC网 > PDF目录17109 > EVAL-ADUC7023QSPZ (Analog Devices Inc)KIT DEV FOR ADUC7023 QUICK START PDF资料下载

参数资料

| 型号: | EVAL-ADUC7023QSPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 53/96页 |

| 文件大小: | 0K |

| 描述: | KIT DEV FOR ADUC7023 QUICK START |

| 标准包装: | 1 |

| 类型: | MCU |

| 适用于相关产品: | ARM7TDMI |

| 所含物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页当前第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页

Data Sheet

ADuC7023

| Page 57 of 96

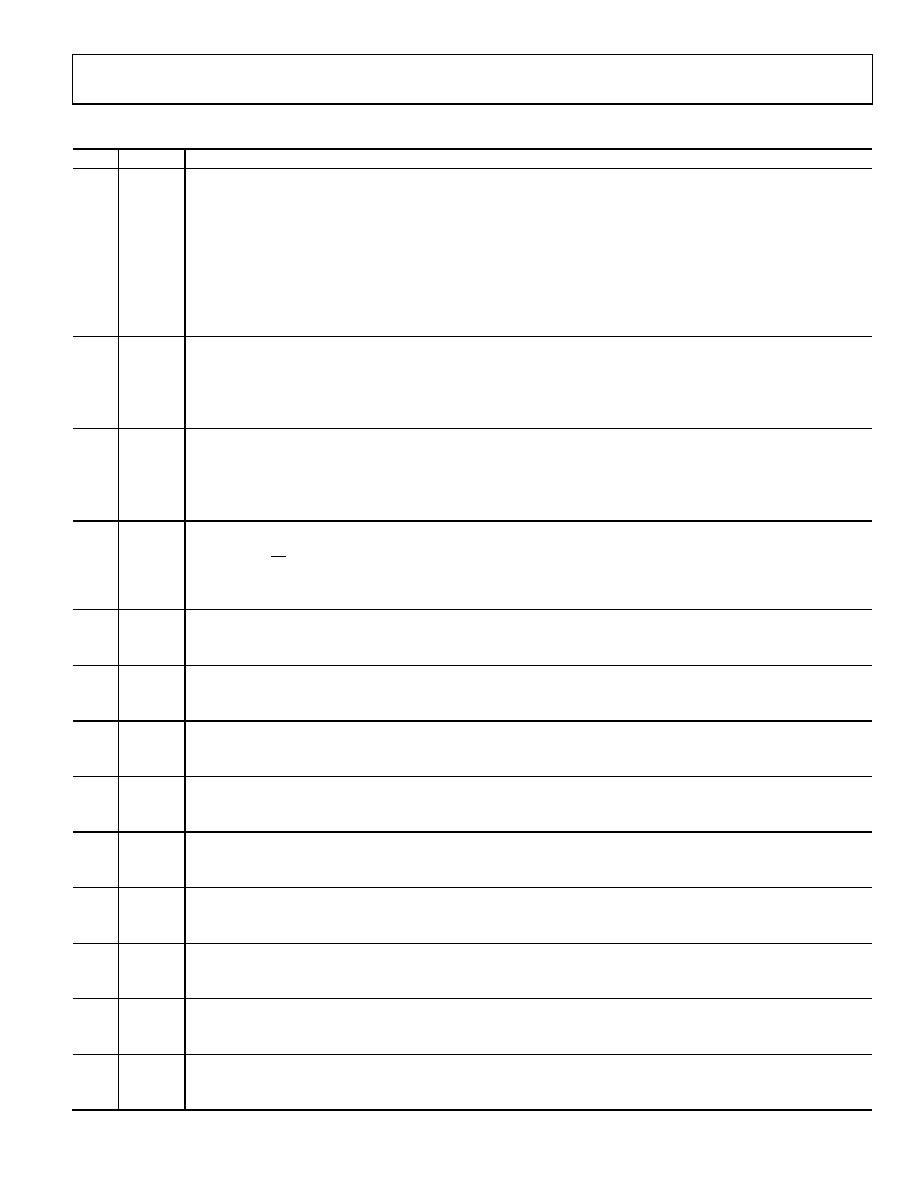

Table 64. SPICON MMR Bit Designations

Bit

Name

Description

15 to

14

SPIMDE

SPI IRQ mode bits. These bits configure when the Tx/Rx interrupts occur in a transfer.

[00] = Tx interrupt occurs when one byte has been transferred. Rx interrupt occurs when one or more bytes have been

received into the FIFO.

[01] = Tx interrupt occurs when two bytes has been transferred. Rx interrupt occurs when two or more bytes have been

received into the FIFO.

[10] = Tx interrupt occurs when three bytes has been transferred. Rx interrupt occurs when three or more bytes have

been received into the FIFO.

[11] = Tx interrupt occurs when four bytes has been transferred. Rx interrupt occurs when the Rx FIFO is full or four bytes

present.

13

SPITFLH

SPI Tx FIFO flush enable bit.

This bit is set to flush the Tx FIFO. This bit does not clear itself and should be toggled if a single flush is required.

If this bit is left high, then either the last transmitted value or 0x00 is transmitted depending on the SPIZEN bit.

Any writes to the Tx FIFO are ignored while this bit is set.

This bit is cleared to disable Tx FIFO flushing.

12

SPIRFLH

SPI Rx FIFO flush enable bit.

This bit is set to flush the Rx FIFO. This bit does not clear itself and should be toggled if a single flush is required.

If this bit is set, all incoming data is ignored and no interrupts are generated.

If set and SPITMDE = 0, a read of the Rx FIFO initiates a transfer.

This bit is cleared to disable Rx FIFO flushing.

11

SPICONT

Continuous transfer enable.

This bit is set by the user to enable continuous transfer. In master mode, the transfer continues until no valid data is available in

the Tx register. SS is asserted and remains asserted for the duration of each 8-bit serial transfer until Tx is empty.

This bit is cleared by the user to disable continuous transfer. Each transfer consists of a single 8-bit serial transfer.

If valid data exists in the SPITX register, then a new transfer is initiated after a stall period of 1 serial clock cycle.

10

SPILP

Loop back enable bit.

This bit is set by the user to connect MISO to MOSI and test software.

This bit is cleared by the user to be in normal mode.

9

SPIOEN

Slave MISO output enable bit.

This bit is set for MISO to operate as normal.

This bit is cleared to disable the output driver on the MISO pin. The MISO pin is open-drain when this bit is clear.

8

SPIROW

SPIRX overflow overwrite enable.

This bit is set by the user; the valid data in the Rx register is overwritten by the new serial byte received.

This bit is cleared by the user; the new serial byte received is discarded.

7

SPIZEN

SPI transmit zeros when Tx FIFO is empty.

This bit is set to transmit 0x00 when there is no valid data in the Tx FIFO.

This bit is cleared to transmit the last transmitted value when there is no valid data in the Tx FIFO.

6

SPITMDE

SPI transfer and interrupt mode.

This bit is set by the user to initiate transfer with a write to the SPITX register. Interrupt only occurs when Tx is empty.

This bit is cleared by the user to initiate transfer with a read of the SPIRX register. Interrupt only occurs when Rx is full.

5

SPILF

LSB first transfer enable bit.

This bit is set by the user; the LSB is transmitted first.

This bit is cleared by the user; the MSB is transmitted first.

4

SPIWOM

SPI wired or mode enable bit.

This bit is set to 1 enable open-drain data output. External pull-ups are required on data out pins.

This bit is cleared for normal output levels.

3

SPICPO

Serial clock polarity mode bit.

This bit is set by the user; the serial clock idles high.

This bit is cleared by the user; the serial clock idles low.

2

SPICPH

Serial clock phase mode bit.

This bit is set by the user; the serial clock pulses at the beginning of each serial bit transfer.

This bit is cleared by the user; the serial clock pulses at the end of each serial bit transfer.

Rev. E

相关PDF资料 |

PDF描述 |

|---|---|

| RPS-1K-6-250/2.0-9 | HEAT SHRINK SLEEVE |

| ECM30DCWH | CONN EDGECARD 60POS DIP .156 SLD |

| SC43B-3R3 | INDUCTOR SMD 3.3UH 1.44A 7.96MHZ |

| EVAL-ADUC842QSPZ | KIT DEV QUICK START ADUC842 |

| EVAL-ADUC841QSPZ | KIT DEV QUICK START ADUC841 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC7023QSPZ1 | 功能描述:BOARD EVAL FOR ADUC7023 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:QuickStart™ PLUS 套件 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| EVAL-ADuC7023QSPZ2 | 制造商:AD 制造商全称:Analog Devices 功能描述:Precision Analog Microcontroller, 12-Bit Analog I/O, ARM7TDMI MCU with Enhanced IRQ Handler |

| EVALADUC7023QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVAL-ADUC7024QS | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Bulk |

| EVAL-ADUC7024QS-U2 | 制造商:Analog Devices 功能描述:QUICK START DEVL SYST EVAL BOARD I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。