- 您现在的位置:买卖IC网 > Datasheet目录369 > W9751G6IB-25 (Winbond Electronics)IC DDR2-800 SDRAM 512MB 84-WBGA Datasheet资料下载

参数资料

| 型号: | W9751G6IB-25 |

| 厂商: | Winbond Electronics |

| 文件页数: | 41/86页 |

| 文件大小: | 0K |

| 描述: | IC DDR2-800 SDRAM 512MB 84-WBGA |

| 标准包装: | 210 |

| 格式 - 存储器: | RAM |

| 存储器类型: | DDR2 SDRAM |

| 存储容量: | 512M(32Mx16) |

| 速度: | 2.5ns |

| 接口: | 并联 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 84-TFBGA |

| 供应商设备封装: | 84-WBGA(8x12.5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

�� �

�

�

�W9751G6IB�

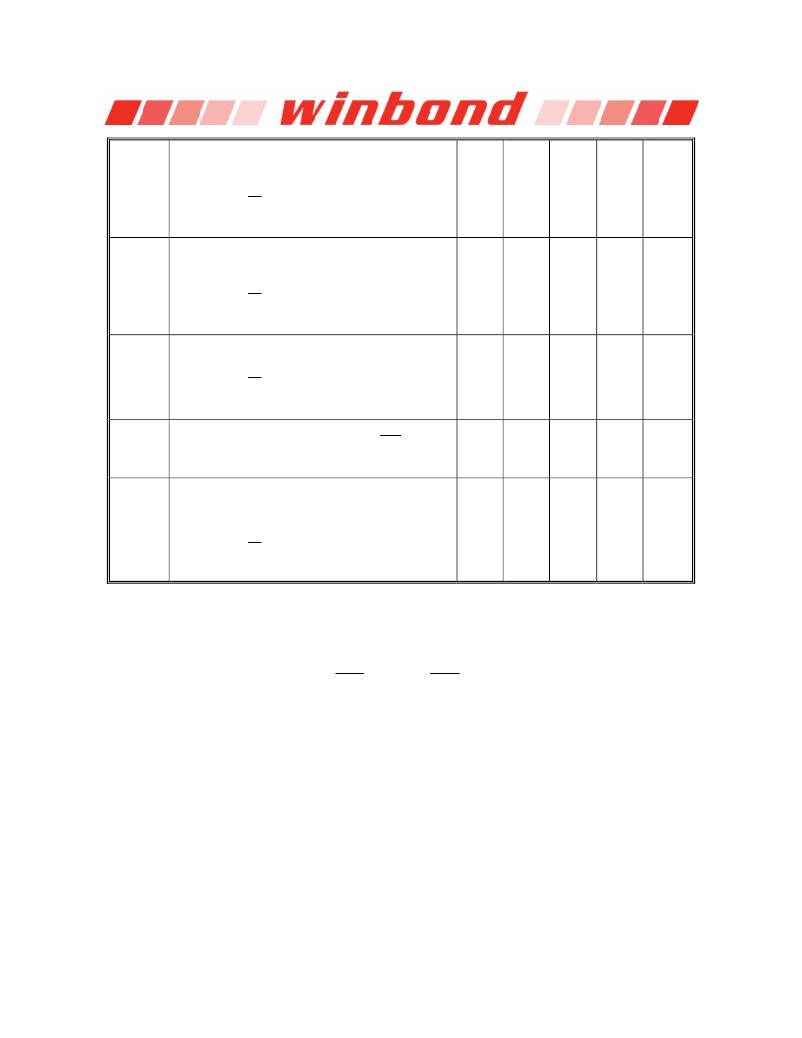

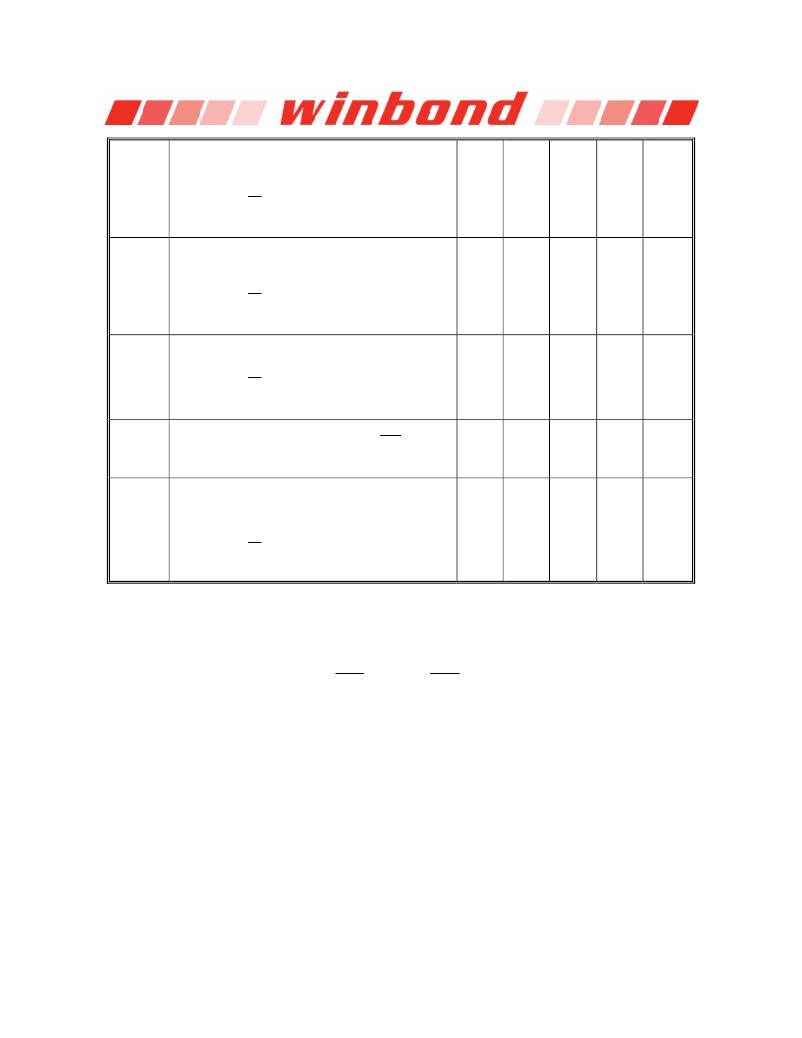

�Operating� Burst� Read� Current�

�All� banks� open,� Continuous� burst� reads,� I� OUT� =� 0� mA;�

�I� DD4R�

�BL� =� 4,� CL� =� CL� (IDD),� AL� =� 0;�

�t� CK� =� t� CK(IDD)� ;� t� RAS� =� t� RASmax(IDD)� ,� t� RP� =� t� RP(IDD)� ;�

�CKE� is� HIGH,� CS� is� HIGH� between� valid� commands;�

�176�

�176�

�155�

�mA�

�1,2,3,4,�

�5,6�

�Address� inputs� are� SWITCHING;�

�Data� Bus� inputs� are� SWITCHING.�

�Operating� Burst� Write� Current�

�All� banks� open,� Continuous� burst� writes;�

�I� DD4W�

�BL� =� 4,� CL� =� CL� (IDD),� AL� =� 0;�

�t� CK� =� t� CK(IDD)� ;� t� RAS� =� t� RASmax(IDD)� ,� t� RP� =� t� RP(IDD)� ;�

�CKE� is� HIGH,� CS� is� HIGH� between� valid� commands;�

�175�

�175�

�160�

�mA�

�1,2,3,4,�

�5,6�

�Address� inputs� are� SWITCHING;�

�Data� Bus� inputs� are� SWITCHING.�

�Burst� Refresh� Current�

�t� CK� =� t� CK(IDD)� ;�

�I� DD5B�

�Refresh� command� every� t� RFC(IDD)� interval;�

�CKE� is� HIGH,� CS� is� HIGH� between� valid� commands;�

�135�

�135�

�125�

�mA�

�1,2,3,4,�

�5,6�

�Other� control� and� address� inputs� are� SWITCHING;�

�Data� bus� inputs� are� SWITCHING.�

�Self� Refresh� Current�

�I� DD6�

�CKE� ≦� 0.2� V,� external� clock� off,� CLK� and� CLK� at� 0� V;�

�Other� control� and� address� inputs� are� FLOATING;�

�7�

�7�

�7�

�mA�

�1,2,3,4,�

�5,6�

�Data� bus� inputs� are� FLOATING.�

�Operating� Bank� Interleave� Read� Current�

�All� bank� interleaving� reads,� I� OUT� =� 0mA;�

�BL� =� 4,� CL� =� CL� (IDD),� AL� =� t� RCD(IDD)� -� 1� x� t� CK(IDD)� ;�

�I� DD7�

�t� CK� =� t� CK(IDD)� ,� t� RC� =� t� RC(IDD)� ,� t� RRD� =� t� RRD(IDD)� ,� t� RCD� =�

�t� RCD(IDD)� ;�

�300�

�300�

�290�

�mA�

�1,2,3,4,�

�5,6�

�CKE� is� HIGH,� CS� is� HIGH� between� valid� commands;�

�Address� bus� inputs� are� STABLE� during� deselects;�

�Data� Bus� inputs� are� SWITCHING.�

�Notes:�

�1.�

�2.�

�3.�

�4.�

�V� DD� =� 1.8� V� ±� 0.1V;� V� DDQ� =� 1.8� V� ±� 0.1V.�

�I� DD� specifications� are� tested� after� the� device� is� properly� initialized.�

�Input� slew� rate� is� specified� by� AC� Parametric� Test� Condition.�

�I� DD� parameters� are� specified� with� ODT� disabled.�

�5.� Data� Bus� consists� of� DQ,� LDM,� UDM,� LDQS,� LDQS� ,� UDQS� and� UDQS� .�

�6.� Definitions� for� I� DD�

�LOW� =� V� in� ≦� V� IL� (ac)� (max)�

�HIGH� =� V� in� ≧� V� IH� (ac)� (min)�

�STABLE� =� inputs� stable� at� a� HIGH� or� LOW� level�

�FLOATING� =� inputs� at� V� REF� =� V� DDQ� /2�

�SWITCHING� =� inputs� changing� between� HIGH� and� LOW� every� other� clock� cycle� (once� per� two� clocks)� for� address� and�

�control� signals,� and� inputs� changing� between� HIGH� and� LOW� every� other� data� transfer� (once� per� clock)�

�for� DQ� signals� not� including� masks� or� strobes.�

�Publication� Release� Date:� Oct.� 23,� 2009�

�-� 41� -�

�Revision� A06�

�相关PDF资料 |

PDF描述 |

|---|---|

| W9751G6KB-25 | IC DDR2 SDRAM 512MBIT 84WBGA |

| W9812G6JH-6I | IC SDRAM 128MBIT 54TSOPII |

| W9816G6IH-6I | IC SDRAM 16MBIT 50TSOPII |

| W9825G6JH-6I | IC SDRAM 256MBIT 54TSOPII |

| W9864G6JH-6I | IC SDRAM 64MBIT 54TSOPII |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9751G6JB | 制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 16 BIT DDR2 SDRAM |

| W9751G6JB-25 | 制造商:Winbond Electronics Corp 功能描述:512GB DDRII |

| W9751G6JB-3 | 制造商:Winbond Electronics Corp 功能描述:512MB DDRII |

| W9751G6KB | 制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 16 BIT DDR2 SDRAM |

| W9751G6KB-18 | 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

发布紧急采购,3分钟左右您将得到回复。