- 您现在的位置:买卖IC网 > PDF目录294782 > A1425A-STDCQ132B FPGA, 310 CLBS, 7500 GATES, 100 MHz, CQFP132 PDF资料下载

参数资料

| 型号: | A1425A-STDCQ132B |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 310 CLBS, 7500 GATES, 100 MHz, CQFP132 |

| 封装: | CERAMIC, QFP-132 |

| 文件页数: | 28/54页 |

| 文件大小: | 343K |

| 代理商: | A1425A-STDCQ132B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

RadTolerant FPGAs

1- 30

v3.1

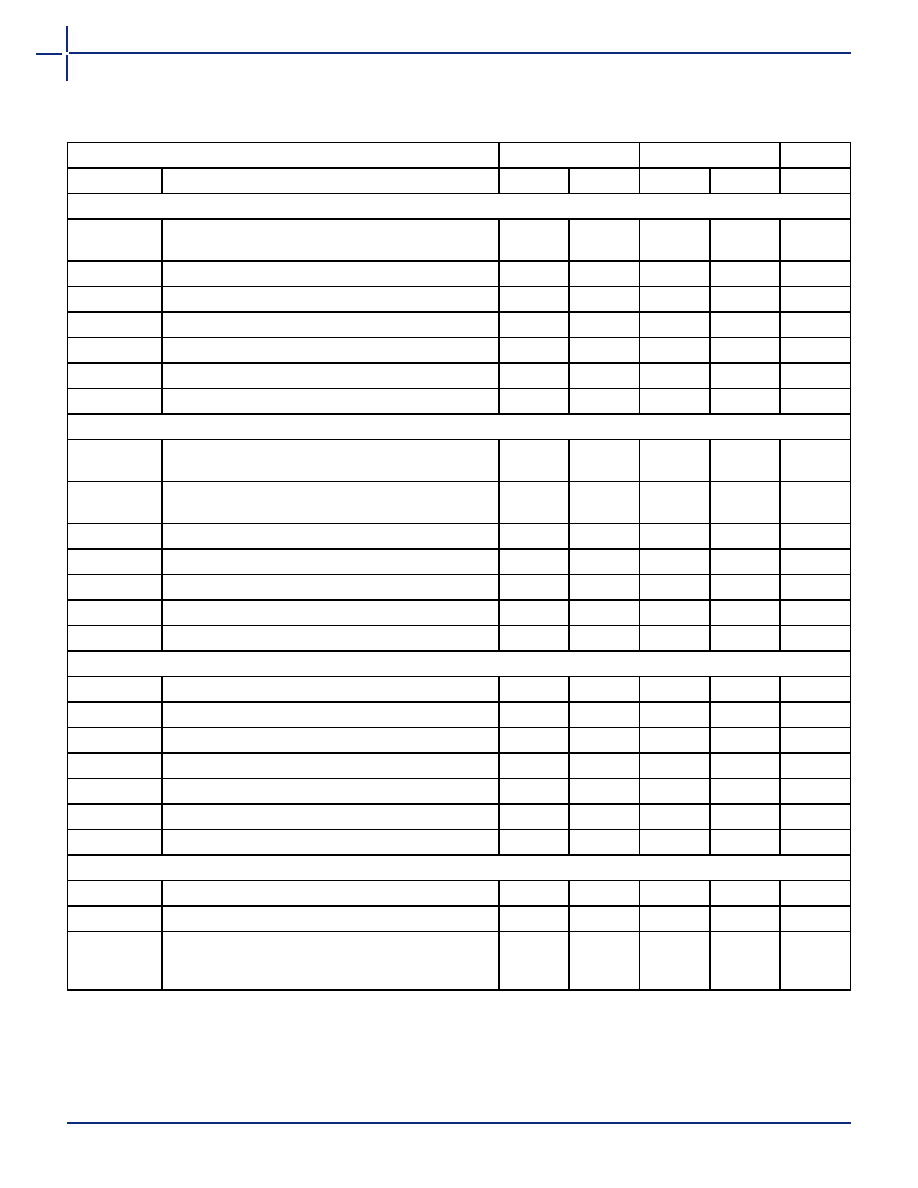

Table 1-23 RT14100A, A14100A Clock Networks

Worst-Case Military Conditions, VCC = 4.5 V, TJ = 125°C

–1 Speed

Std Speed

Parameter

Description

Min.

Max.

Min.

Max.

Units

Dedicated (Hard-Wired) I/O Clock Network

tIOCKH

Input LOW to HIGH

(Pad to I/O Module Input)

3.5

4.1

ns

tIOPWH

Minimum Pulse Width HIGH

4.8

5.7

ns

tIOPWL

Minimum Pulse Width LOW

4.8

5.7

ns

tIOSAPW

Minimum Asynchronous Pulse Width

3.9

4.4

ns

tIOCKSW

Maximum Skew

0.9

1.0

ns

tIOP

Minimum Period

9.9

11.6

ns

fIOMAX

Maximum Frequency

100

85

MHz

Dedicated (Hard-Wired) Array Clock Network

tHCKH

Input LOW to HIGH

(Pad to S-Module Input)

5.5

6.4

ns

tHCKL

Input HIGH to LOW

(Pad to S-Module Input)

5.5

6.4

ns

tHPWH

Minimum Pulse Width HIGH

4.8

5.7

ns

tHPWL

Minimum Pulse Width LOW

4.8

5.7

ns

tHCKSW

Maximum Skew

0.9

1.0

ns

tHP

Minimum Period

9.9

11.6

ns

fHMAX

Maximum Frequency

100

85

MHz

Routed Array Clock Networks

tRCKH

Input LOW to HIGH (FO=256)

9.0

10.5

ns

tRCKL

Input HIGH to LOW (FO=256)

9.0

10.5

ns

tRPWH

Min. Pulse Width HIGH (FO=256)

6.3

7.1

ns

tRPWL

Min. Pulse Width LOW (FO=256)

6.3

7.1

ns

tRCKSW

Maximum Skew (FO=128)

1.9

2.1

ns

tRP

Minimum Period (FO=256)

12.9

14.5

ns

fRMAX

Maximum Frequency (FO=256)

75

65

MHz

Clock-to-Clock Skews

tIOHCKSW

I/O Clock to H-Clock Skew

0.0

3.5

0.0

3.5

ns

tIORCKSW

I/O Clock to R-Clock Skew

0.0

5.0

0.0

5.0

ns

tHRCKSW

H-Clock to R-Clock Skew

(FO = 64)

(FO = 50% max.)

0.0

1.0

3.0

0.0

1.0

3.0

ns

Note: SSO information can be found in the Simultaneously Switching Output Limits for Actel FPGAs application note.

相关PDF资料 |

PDF描述 |

|---|---|

| A1425A-STDCQ132C | FPGA, 310 CLBS, 7500 GATES, CQFP132 |

| A1425A-STDCQ132M | FPGA, 310 CLBS, 7500 GATES, 100 MHz, CQFP132 |

| A14100A-STDCQG256B | FPGA, 1377 CLBS, 30000 GATES, 85 MHz, CQFP256 |

| A14100A-STDCQG256M | FPGA, 1377 CLBS, 30000 GATES, 85 MHz, CQFP256 |

| A1460A-1PQ160M | FPGA, 848 CLBS, 6000 GATES, 125 MHz, PQFP160 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A1425A-STDCQ132M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:ASIC |

| A1425A-VQ100C | 功能描述:IC FPGA 2500 GATES 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ACT™ 3 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| A1425A-VQ100I | 功能描述:IC FPGA 2500 GATES 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ACT™ 3 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| A1425A-VQG100C | 功能描述:IC FPGA 2500 GATES 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ACT™ 3 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| A1425A-VQG100I | 功能描述:IC FPGA 2500 GATES 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ACT™ 3 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

发布紧急采购,3分钟左右您将得到回复。