- 您现在的位置:买卖IC网 > PDF目录16490 > AD6641-500EBZ (Analog Devices Inc)BOARD EVALUATION FOR AD6641 PDF资料下载

参数资料

| 型号: | AD6641-500EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/28页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD6641 |

| 设计资源: | AD6641 BOM |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD6641

Rev. 0 | Page 11 of 28

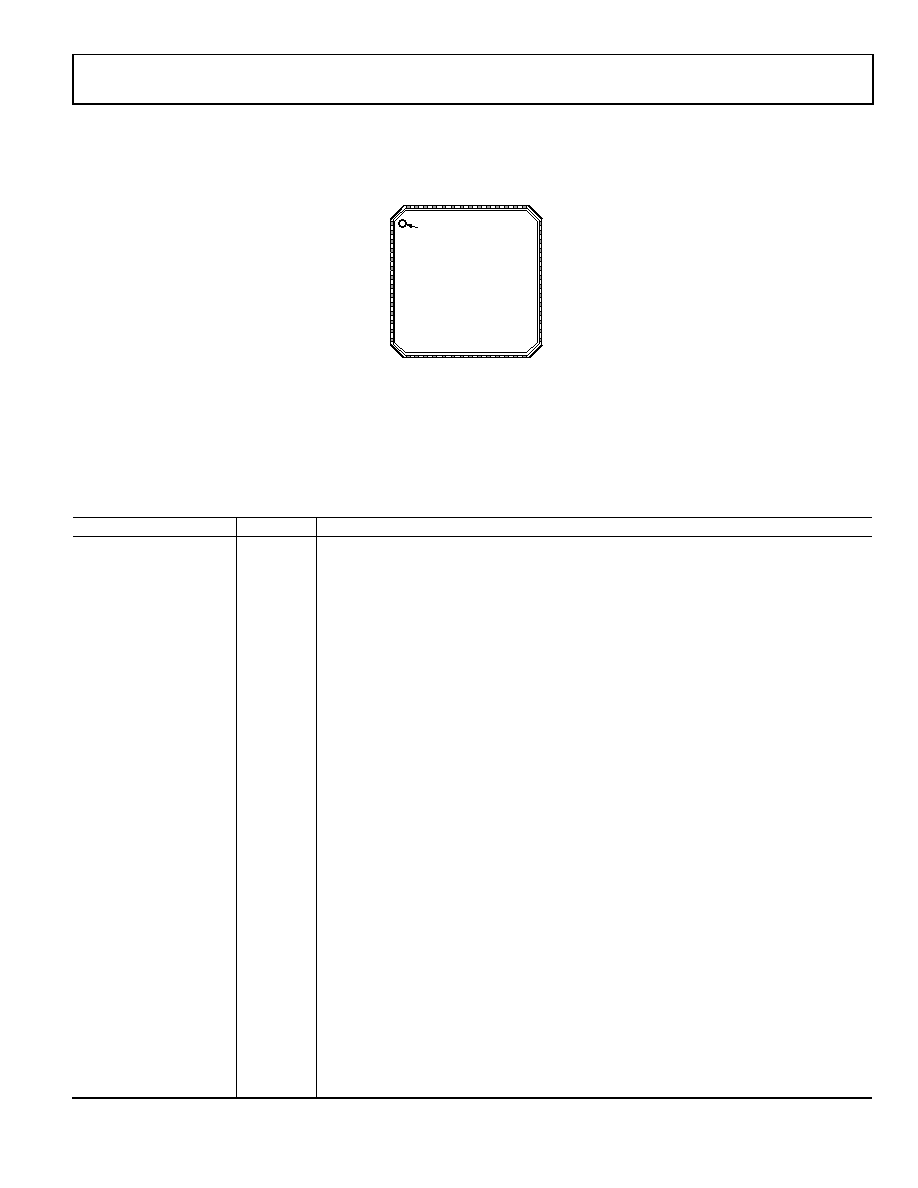

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

FU

LL

EMPTY

PD1–

VIN+

VIN–

AVDD

CML

AVDD

NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

2. THE EXPOSED PAD IS THE ONLY ANALOG GROUND

CONNECTION FOR THE CHIP. IT MUST BE CONNECTED TO PCB AGND.

AVDD

VREF

AVDD

PD

OR–

CL

K–

AVD

D

DR

VDD

DR

G

ND

FIL

L

–

FIL

L

+

DU

MP

CL

K+

AVD

D

PCLK–

PCLK+

DN

C

SPI_VDDIO

PD0–

PD0+

PD1+

PD2–

PD2+

DRVDD

DRGND

PD3–

PD3+

PD4–

PD4+

PD5–

PD5+

PD

O

R

+

SP_SDO

DN

C

DN

C

DN

C

SP_SD

F

S

SP_SCLK

DRG

N

D

DR

V

DD

SDIO SCLK CS

B

DN

C

PIN 1

INDICATOR

1

2

3

4

5

6

7

8

9

10

11

12

13

14

35

36

37

38

39

40

41

42

34

33

32

31

30

29

51 61 71

91

12

02

22 32 42 52 62 72 82

81

54

64

74

84

94

05

15

25

35

45

44 34

AD6641

55

65

TOP VIEW

(Not to Scale)

0

981

3-0

08

Figure 8. Pin Configuration for DDR LVDS Mode

Table 8. DDR LVDS Mode Pin Function Descriptions

Pin No.

Mnemonic

Description

0

EPAD

Exposed Pad. The exposed pad is the only ground connection for the chip. The pad must be

connected to PCB AGND.

1

PD0

PD0 Data Output (LSB)—Complement.

2

PD0+

PD0 Data Output (LSB)—True.

3

PD1

PD1 Data Output—Complement.

4

PD1+

PD1 Data Output—True.

5

PD2

PD2 Data Output—Complement.

6

PD2+

PD2 Data Output—True.

7, 24, 47

DRVDD

1.9 V Digital Output Supply.

8, 23, 48

DRGND

Digital Output Ground.

9

PD3

PD3 Data Output—Complement.

10

PD3+

PD3 Data Output—True.

11

PD4

PD4 Data Output—Complement.

12

PD4+

PD4 Data Output—True.

13

PD5

PD5 Data Output (MSB)—Complement.

14

PD5+

PD5 Data Output (MSB)—True.

15

PDOR

Overrange Output—Complement.

16

PDOR+

Overrange Output—True.

17

SP_SDO

SPORT Output.

18, 19, 20, 28, 54

DNC

Do Not Connect. Do not connect to this pin.

21

SP_SDFS

SPORT Frame Sync Input (Slave Mode)/Output (Master Mode).

22

SP_SCLK

SPORT Clock Input (Slave Mode)/Output (Master Mode).

25

SDIO

Serial Port Interface (SPI) Data Input/Output (Serial Port Mode).

26

SCLK

Serial Port Interface Clock (Serial Port Mode).

27

CSB

Serial Port Chip Select (Active Low).

29

SPI_VDDIO

1.9 V or 3.3 V SPI I/O Supply.

30, 32, 33, 34, 37, 38, 39,

41, 42, 43, 46

AVDD

1.9 V Analog Supply.

31

VREF

Voltage Reference Input/Output. Nominally 0.75 V.

35

VIN+

Analog Input—True.

36

VIN

Analog Input—Complement.

相关PDF资料 |

PDF描述 |

|---|---|

| EBM30DTBD | CONN EDGECARD 60POS R/A .156 SLD |

| HCC07DRTH-S93 | CONN EDGECARD 14POS DIP .100 SLD |

| 1906051-8 | CA 2MM OFNR 62.5/125,LC SEC RED |

| 1828875-2 | C/A FO LC SEC SC BLUE 62.5 2M |

| A3932SEQ-T | IC CTRLR MOSFET 3PH 32-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6641BCPZ-500 | 功能描述:IC IF RCVR 11BIT 200MSPS 56LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6641BCPZRL7-500 | 功能描述:IC IF RCVR 11BIT 200MSPS 56LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6642 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual IF Receiver |

| AD6642BBCZ | 功能描述:IC IF RCVR 11BIT 200MSPS 144BGA RoHS:是 类别:RF/IF 和 RFID >> RF 其它 IC 和模块 系列:- 标准包装:100 系列:* |

| AD6642BBCZRL | 功能描述:IC IF RCVR 11BIT 200MSPS 144BGA RoHS:是 类别:RF/IF 和 RFID >> RF 其它 IC 和模块 系列:- 标准包装:100 系列:* |

发布紧急采购,3分钟左右您将得到回复。