- 您现在的位置:买卖IC网 > PDF目录298476 > 70P249L65BYGI (INTEGRATED DEVICE TECHNOLOGY INC) 4K X 16 DUAL-PORT SRAM, 40 ns, PBGA100 PDF资料下载

参数资料

| 型号: | 70P249L65BYGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | SRAM |

| 英文描述: | 4K X 16 DUAL-PORT SRAM, 40 ns, PBGA100 |

| 封装: | 0.50 MM PITCH, GREEN, BGA-100 |

| 文件页数: | 3/22页 |

| 文件大小: | 146K |

| 代理商: | 70P249L65BYGI |

6.42

11

IDT70P269/259/249L

Low Power 16K/8K/4K x 16 Dual-Port Static RAM

Industrial Temperature Range

OCTOBER 16, 2008

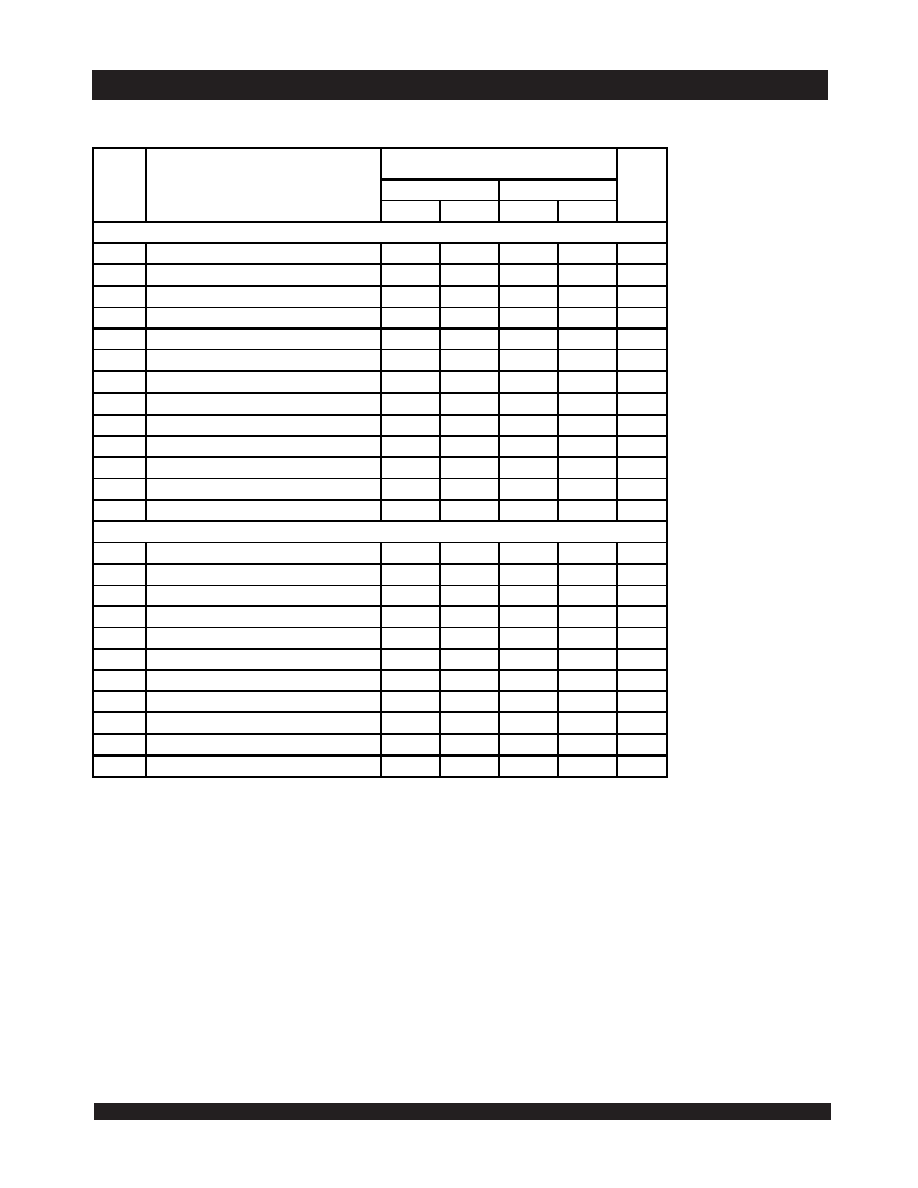

AC Electrical Characteristics Over the

Operating Temperature and Supply Voltage Range(1)

Symbol

Parameter

70P269/259/249

Unit

65 ns

90 ns

Min.

Max.

Min.

Max..

ADM Port Write Cycle

(2)

tWC

Write Cycle Time

65

____

90

____

ns

tSCS

CS Low to Write End

65

____

90

____

ns

tAVD

ADV Low Pulse

15

____

20

____

ns

tAVDS

Address Set-up to

ADV Rising Edge

15

____

20

____

ns

tAVDH

Address Hold from

ADV Rising Edge

3

____

5

____

ns

tCSS

CS Set-up to ADV Rising Edge

7

____

10

____

ns

tWRL

WE Pulse Width

28

____

45

____

ns

tBW

UB/LB Low to Write End

28

____

45

____

ns

tSD

Data Set-up to Write End

20

____

30

____

ns

tHD

Data Hold from Write End

0

____

0

____

ns

tLZWE(3)

WE High to I/O Low-Z

0

____

0

____

ns

tAVWE

ADV High to WE Low

0

____

0

____

ns

tWODR

Write End to ODR Valid

____

40

____

60

ns

Standard Port Write Cycle (4)

tWC

Write Cycle Time

40

____

60

____

ns

tSCS

CS Low to Write End

30

____

50

____

ns

tAW

Address Valid to Write End

30

____

50

____

ns

tHA

Address Hold to Write End

0

____

0

____

ns

tSA

Address Set-up to Write Start

0

____

0

____

ns

tWRL

Write Pulse Width

25

____

45

____

ns

tSD

Data Set-up to Write End

20

____

30

____

ns

tHD

Data Hold from Write End

0

____

0

____

ns

tHZWE

(3)

WE Low to Data High-Z

____

15

____

25

ns

tLZWE(3)

WE High to Data Low-Z

0

____

0

____

ns

tWODR

Write End to ODR Valid

____

40

____

60

ns

7146 tbl 13

NOTES:

1. VDD = 1.8V

2. ADM port timing applies to the left or right port when configured to ADM mode.

3. This parameter is guaranteed by design and is not tested.

4. Standard SRAM port timing applies to the left or right port when configured to standard SRAM mode.

相关PDF资料 |

PDF描述 |

|---|---|

| 70R89-P | 20 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 70R89-59 | 20 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 70R89-58 | 20 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 70R89-50 | 20 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 70R89-49 | 20 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 70P249L65BYGI8 | 功能描述:静态随机存取存储器 Low Power Dual-Port RAM IC RoHS:否 制造商:IDT 存储容量: 组织: 访问时间: 电源电压-最大: 电源电压-最小: 最大工作电流: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: |

| 70P249L90BYGI | 功能描述:IC SRAM 64KBIT 90NS 100FBGA 制造商:idt, integrated device technology inc 系列:- 包装:托盘 零件状态:过期 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:64K(4K x 16) 速度:90ns 接口:并联 电压 - 电源:1.7 V ~ 1.9 V 工作温度:-40°C ~ 85°C(TA) 封装/外壳:100-TFBGA 供应商器件封装:100-CABGA(6x6) 标准包装:90 |

| 70P249L90BYGI8 | 功能描述:静态随机存取存储器 Low Power Dual-Port RAM IC RoHS:否 制造商:IDT 存储容量: 组织: 访问时间: 电源电压-最大: 电源电压-最小: 最大工作电流: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: |

| 70P24L20BF | 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 1.8V 64KBIT 4K X 16 20NS 100BGA - Bulk |

| 70P24L20BF8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 1.8V 64KBIT 4K X 16 20NS 100BGA - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。