参数资料

| 型号: | XRT83L38IB |

| 厂商: | Exar Corporation |

| 文件页数: | 24/87页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/E1/J1 OCTAL 225BGA |

| 标准包装: | 84 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 8/8 |

| 规程: | T1,E1,J1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 225-BGA |

| 供应商设备封装: | 225-BGA(19x19) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

XRT83L38

27

OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.0.2

RCLK for all eight channels. Writing a “0” to the RCLKE register, updates the receive data on the rising edge of

RCLK. In Hardware mode the same feature is available under the control of the RCLKE pin.

JITTER ATTENUATOR

To reduce phase and frequency jitter in the recovered clock, the jitter attenuator can be placed in the receive

signal path. The jitter attenuator uses a data FIFO (First In First Out) with a programmable depth that can vary

between 2x32 and 2x64. The jitter attenuator can also be placed in the transmit signal path or disabled

altogether depending upon system requirements. The jitter attenuator, other than using the master clock as

reference, requires no external components. With the jitter attenuator selected, the typical throughput delay

from input to output is 16 bits for 32 bit FIFO size or 32 bits for 64 bit FIFO size. When the read and write

pointers of the FIFO in the jitter attenuator are within two bits of over-flowing or under-flowing, the bandwidth of

the jitter attenuator is widened to track the short term input jitter, thereby avoiding data corruption. When this

situation occurs, the jitter attenuator will not attenuate input jitter until the read/write pointer's position is outside

the two bits window. Under normal condition, the jitter transfer characteristic meets the narrow bandwidth

requirement as specified in ITU- G.736, ITU- I.431 and AT&T Pub 62411 standards.

In T1 mode the Jitter Attenuator Bandwidth is always set to 3Hz. In E1 mode, the bandwidth can be reduced

through the JABW control signal. When JABW is set “High” the bandwidth of the jitter attenuator is reduced

from 10Hz to 1.5Hz. Under this condition the FIFO length is automatically set to 64 bits and the 32 bits FIFO

length will not be available in this mode. Jitter attenuator controls are available on a per channel basis in the

Host mode and on a global basis in the Hardware mode.

GAPPED CLOCK (JA MUST BE ENABLED IN THE TRANSMIT PATH)

The XRT83L38 LIU is ideal for multiplexer or mapper applications where the network data crosses multiple

timing domains. As the higher data rates are de-multiplexed down to T1 or E1 data, stuffing bits are removed

which can leave gaps in the incoming data stream. If the jitter attenuator is enabled in the transmit path, the

32-Bit or 64-Bit FIFO is used to smooth the gapped clock into a steady T1 or E1 output. The maximum gap

width of the 8-Channel LIU is shown in Table 2.

NOTE: If the LIU is used in a loop timing system, the jitter attenuator should be enabled in the receive path.

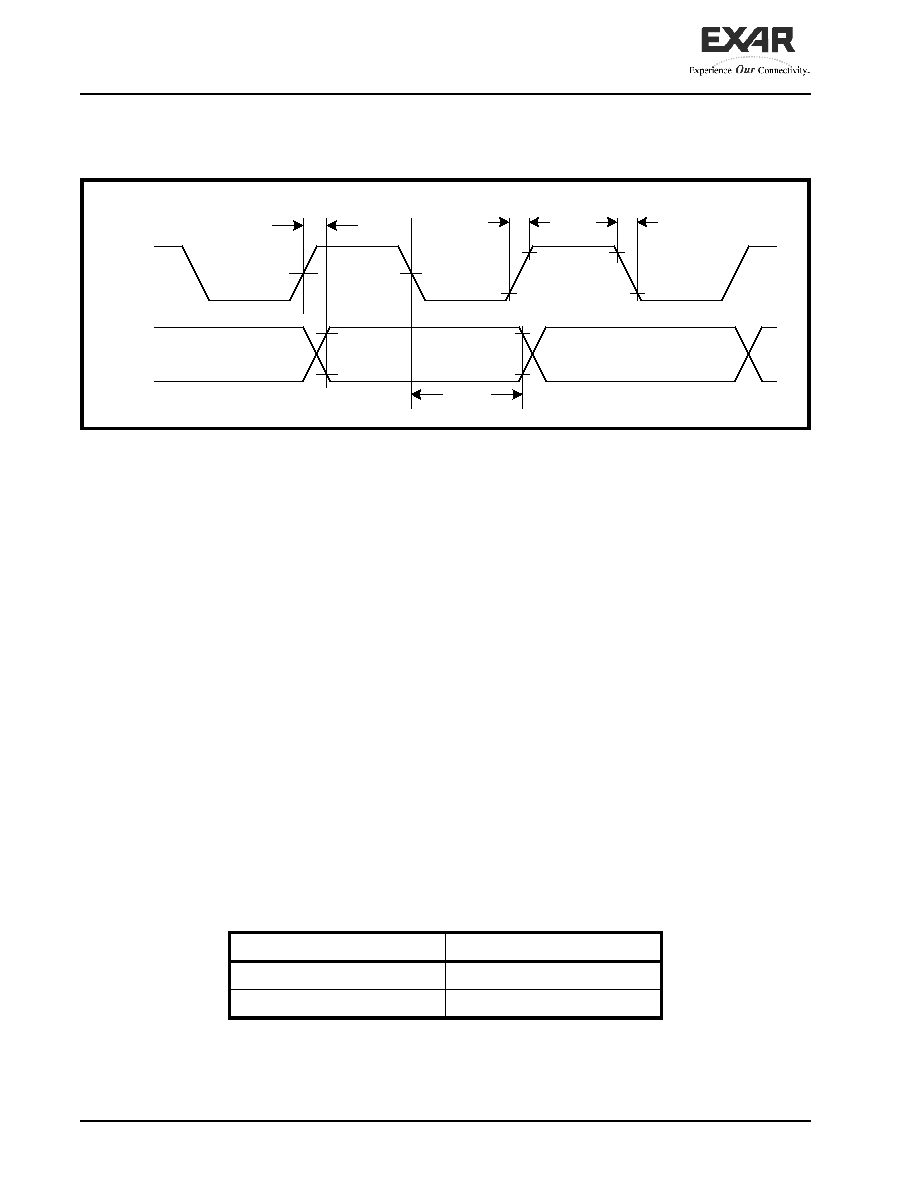

FIGURE 10. RECEIVE CLOCK AND OUTPUT DATA TIMING

TABLE 2: MAXIMUM GAP WIDTH FOR MULTIPLEXER/MAPPER APPLICATIONS

FIFO DEPTH

MAXIMUM GAP WIDTH

32-Bit

20 UI

64-Bit

50 UI

RCLK

R

RCLK

F

RCLK

RPOS

or

RNEG

R

DY

R

HO

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72V3660L10PF8 | IC FIFO SS 4096X36 10NS 128-TQFP |

| MS3101F20-23PW | CONN RCPT 2POS FREE HNG W/PINS |

| XRT75R03DIV | IC LIU E3/DS3/STS-1 3CH 128LQFP |

| ISL26710IHZ-T | IC ADC 10BIT SPI/SRL 1M 8-SOT-23 |

| MS27472T10F35SB | CONN RCPT 13POS WALL MNT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT83L38IB-F | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| XRT83L38IV | 制造商:EXAR 制造商全称:EXAR 功能描述:OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR |

| XRT83SH314 | 制造商:EXAR 制造商全称:EXAR 功能描述:14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT |

| XRT83SH314_0610 | 制造商:EXAR 制造商全称:EXAR 功能描述:14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT |

| XRT83SH314ES | 功能描述:外围驱动器与原件 - PCI 14 CHT1/E1LIU SH RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。