参数资料

| 型号: | XC6SLX75T-2FG676I |

| 厂商: | Xilinx Inc |

| 文件页数: | 45/89页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN 6 676FGGBGA |

| 标准包装: | 40 |

| 系列: | Spartan® 6 LXT |

| LAB/CLB数: | 5831 |

| 逻辑元件/单元数: | 74637 |

| RAM 位总计: | 3170304 |

| 输入/输出数: | 348 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 676-BGA |

| 供应商设备封装: | 676-FBGA(27x27) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页当前第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

Spartan-6 FPGA Data Sheet: DC and Switching Characteristics

DS162 (v3.0) October 17, 2011

Product Specification

5

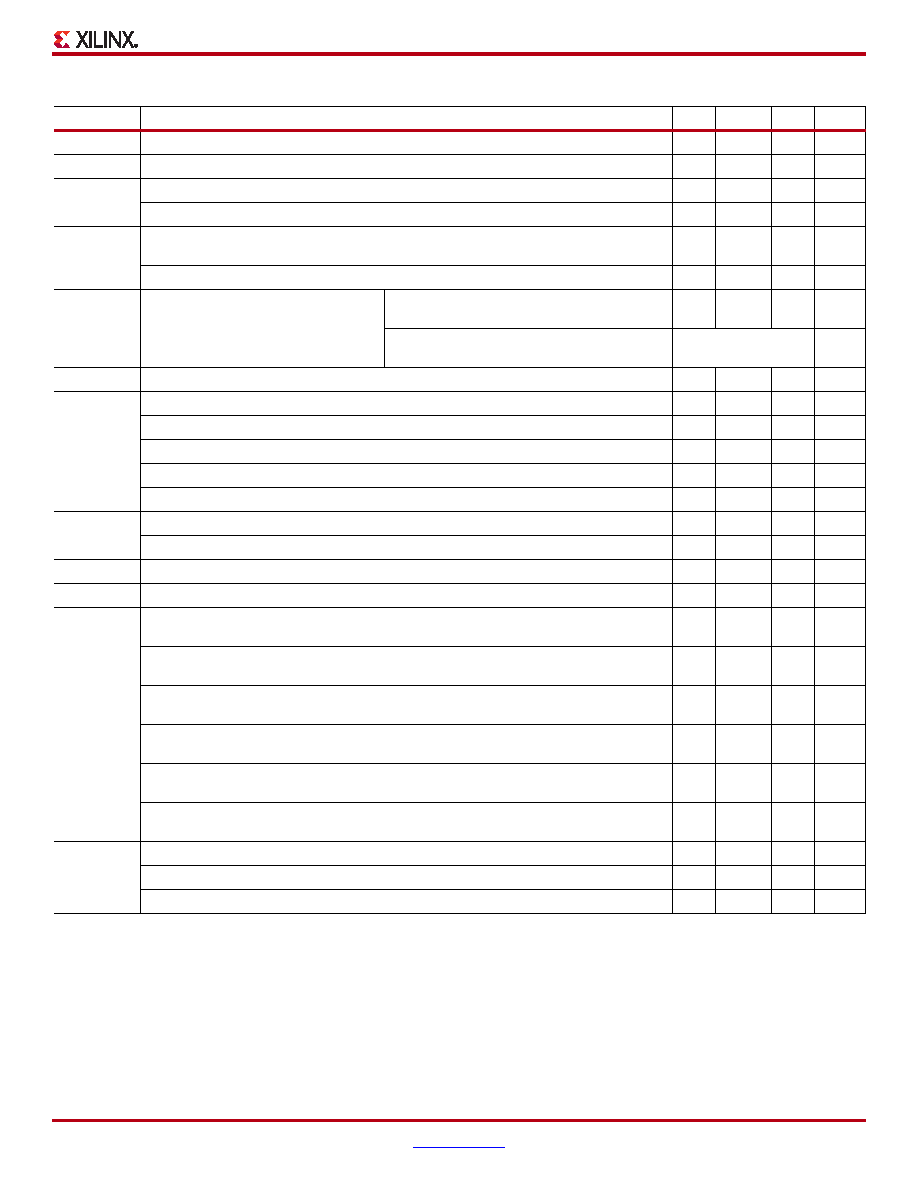

Table 4: DC Characteristics Over Recommended Operating Conditions

Symbol

Description

Min

Typ

Max

Units

VDRINT

Data retention VCCINT voltage (below which configuration data might be lost)

0.8

–

V

VDRAUX

Data retention VCCAUX voltage (below which configuration data might be lost)

2.0

–

V

IREF

VREF leakage current per pin for commercial (C) and industrial (I) devices

–10

–

10

A

VREF leakage current per pin for expanded (Q) devices

–15

–

15

A

IL

Input or output leakage current per pin (sample-tested) for commercial (C) and industrial

(I) devices

–10

–

10

A

Input or output leakage current per pin (sample-tested) for expanded (Q) devices

–15

–

15

A

IHS

Leakage current on pins during hot

socketing with FPGA unpowered

All pins except PROGRAM_B, DONE, and

JTAG pins when HSWAPEN = 1

–20

–

20

A

PROGRAM_B, DONE, and JTAG pins, or other

pins when HSWAPEN = 0

IHS + IRPU

A

CIN(1)

Die input capacitance at the pad

–

10

pF

IRPU

Pad pull-up (when selected) @ VIN =0V, VCCO =3.3V or VCCAUX = 3.3V

200

–

500

A

Pad pull-up (when selected) @ VIN =0V, VCCO =2.5V or VCCAUX = 2.5V

120

–

350

A

Pad pull-up (when selected) @ VIN =0V, VCCO = 1.8V

60

–

200

A

Pad pull-up (when selected) @ VIN =0V, VCCO = 1.5V

40

–

150

A

Pad pull-up (when selected) @ VIN =0V, VCCO = 1.2V

12

–

100

A

IRPD

Pad pull-down (when selected) @ VIN =VCCO, VCCAUX = 3.3V

200

–

550

A

Pad pull-down (when selected) @ VIN =VCCO, VCCAUX = 2.5V

140

–

400

A

IBATT(2)

Battery supply current

–

150

nA

RDT(3)

Resistance of optional input differential termination circuit, VCCAUX =3.3V

–

100

–

RIN_TERM(5)

Thevenin equivalent resistance of programmable input termination to VCCO

(UNTUNED_SPLIT_25) for commercial (C) and industrial (I) devices

23

25

55

Thevenin equivalent resistance of programmable input termination to VCCO

(UNTUNED_SPLIT_25) for expanded (Q) devices

20

25

55

Thevenin equivalent resistance of programmable input termination to VCCO

(UNTUNED_SPLIT_50) for commercial (C) and industrial (I) devices

39

50

72

Thevenin equivalent resistance of programmable input termination to VCCO

(UNTUNED_SPLIT_50) for expanded (Q) devices

32

50

74

Thevenin equivalent resistance of programmable input termination to VCCO

(UNTUNED_SPLIT_75) for commercial (C) and industrial (I) devices

56

75

109

Thevenin equivalent resistance of programmable input termination to VCCO

(UNTUNED_SPLIT_75) for expanded (Q) devices

47

75

115

ROUT_TERM

Thevenin equivalent resistance of programmable output termination (UNTUNED_25)

11

25

52

Thevenin equivalent resistance of programmable output termination (UNTUNED_50)

21

50

96

Thevenin equivalent resistance of programmable output termination (UNTUNED_75)

29

75

145

Notes:

1.

The CIN measurement represents the die capacitance at the pad, not including the package.

2.

Maximum value specified for worst case process at 25°C. LX75, LX75T, LX100, LX100T, LX150, and LX150T only.

3.

Refer to IBIS models for RDT variation and for values at VCCAUX = 2.5V. IBIS values for RDT are valid for all temperature ranges.

4.

VCCO2 is not required for data retention. The minimum VCCO2 for power-on reset and configuration is 1.65V.

5.

Termination resistance to a VCCO/2 level.

相关PDF资料 |

PDF描述 |

|---|---|

| XC6SLX75T-2FGG676I | IC FPGA SPARTAN 6 74K 676FGGBGA |

| ACB100DHHN | CONN EDGECARD 200PS .050 DIP SLD |

| ABB100DHHN | CONN EDGECARD 200PS .050 DIP SLD |

| ACB100DHHD | CONN EDGECARD 200PS .050 DIP SLD |

| ABB100DHHD | CONN EDGECARD 200PS .050 DIP SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC6SLX75T-2FGG484C | 功能描述:IC FPGA SPARTAN 6 74K 484FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| XC6SLX75T-2FGG484I | 功能描述:IC FPGA SPARTAN 6 74K 484FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC6SLX75T-2FGG676C | 功能描述:IC FPGA SPARTAN 6 74K 676FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC6SLX75T-2FGG676I | 功能描述:IC FPGA SPARTAN 6 74K 676FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC6SLX75T-3CSG484C | 功能描述:IC FPGA SPARTAN 6 74K 484CSGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

发布紧急采购,3分钟左右您将得到回复。