- 您现在的位置:买卖IC网 > PDF目录25515 > 951462YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) PROC SPECIFIC CLOCK GENERATOR, PDSO64 PDF资料下载

参数资料

| 型号: | 951462YGLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| 封装: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-64 |

| 文件页数: | 11/23页 |

| 文件大小: | 241K |

| 代理商: | 951462YGLFT |

19

Integrated

Circuit

Systems, Inc.

ICS951462

1094J—03/16/09

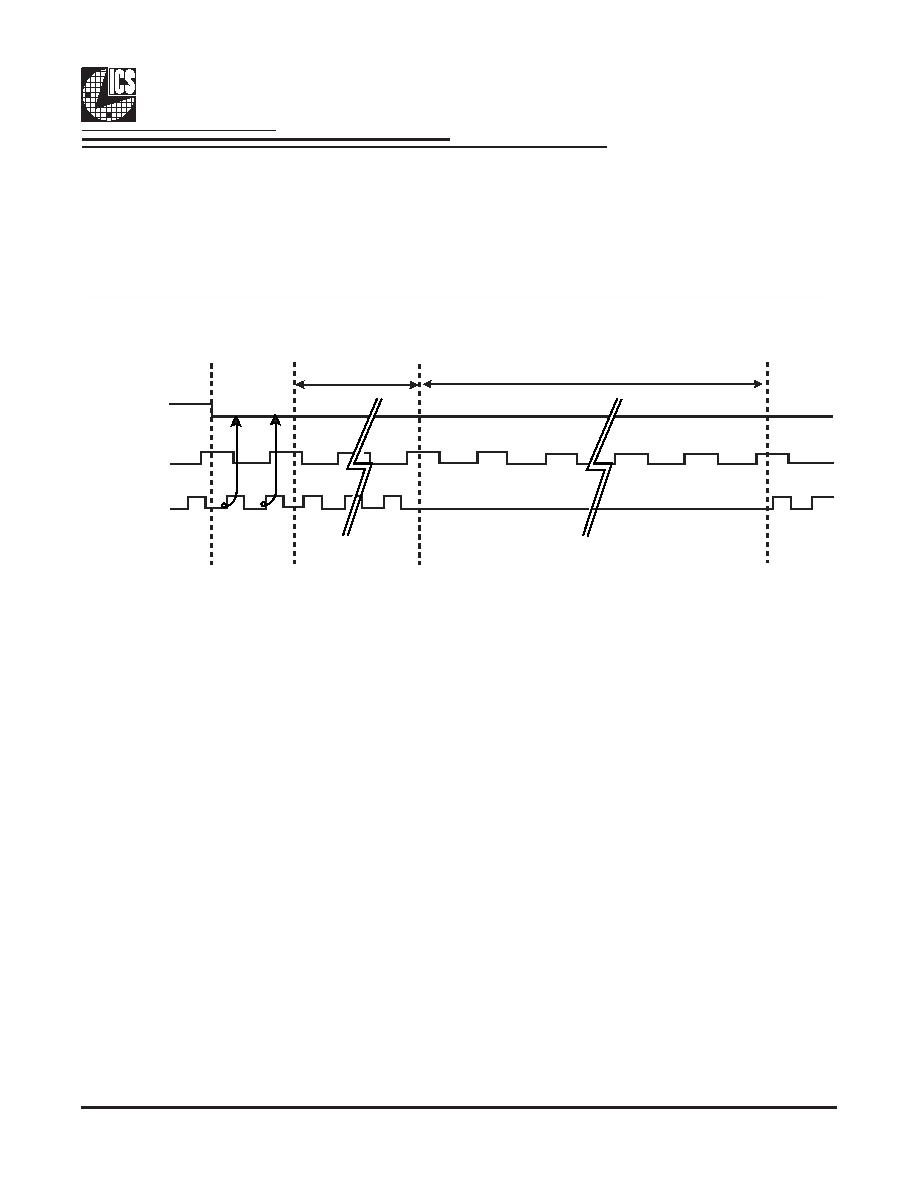

RESET_IN# - Assertion (transition from '1' to '0')

The pin is a Schmitt trigger input with debouncing. After it is triggered, REF clocks will wait for two clock cycle to

Asserting RESET_IN pin stops all the outputs including CPU, SRC, ATIG, PCI and USB with the REF[2:0] running.

be power down and re-power up, and SMBus will be reloaded. It will take no more than 2.5mS for the clocks to come

out with correct frequencies and no glitches.

** Deassertion of RESET_IN# (transition from '0' to '1') has NO effect on the clocks.

ensure the RESET_IN is asserted. Then, it will take 3uS for the clocks to stop without glitches. The clock chip will

2.5mS max

3 uS max

2 clock

cycles

RESET_IN#

REF [2:0]

*CLKS

相关PDF资料 |

PDF描述 |

|---|---|

| 951464YFLFT | 240 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| 951601AFLF | 66.66 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 951901AF | 133.34 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 951901AFLFT | 133.34 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 951 | WIRE TERMINAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 951463AGLF | 制造商:Integrated Device Technology Inc 功能描述:951463AGLF - Rail/Tube |

| 951463BFLF | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK 制造商:Integrated Device Technology Inc 功能描述:56 SSOP (LEAD FREE) - Rail/Tube |

| 951463BFLFT | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK 制造商:Integrated Device Technology Inc 功能描述:56 SSOP (LEAD FREE) - Tape and Reel |

| 951463BGLF | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

| 951463BGLFT | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

发布紧急采购,3分钟左右您将得到回复。