- 您现在的位置:买卖IC网 > PDF目录30702 > 49LF002 (Silicon Storage Technology, Inc.) 2 Mbit / 3 Mbit / 4 Mbit / 8 Mbit Firmware Hub PDF资料下载

参数资料

| 型号: | 49LF002 |

| 厂商: | Silicon Storage Technology, Inc. |

| 英文描述: | 2 Mbit / 3 Mbit / 4 Mbit / 8 Mbit Firmware Hub |

| 中文描述: | 2兆位/ 3兆/ 4兆位/ 8兆固件集线器 |

| 文件页数: | 17/36页 |

| 文件大小: | 412K |

| 代理商: | 49LF002 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

24

Advance Information

2 Mbit / 3 Mbit / 4 Mbit / 8 Mbit Firmware Hub

SST49LF002A / SST49LF003A / SST49LF004A / SST49LF008A

2001 Silicon Storage Technology, Inc.

S71161-06-000

9/01

504

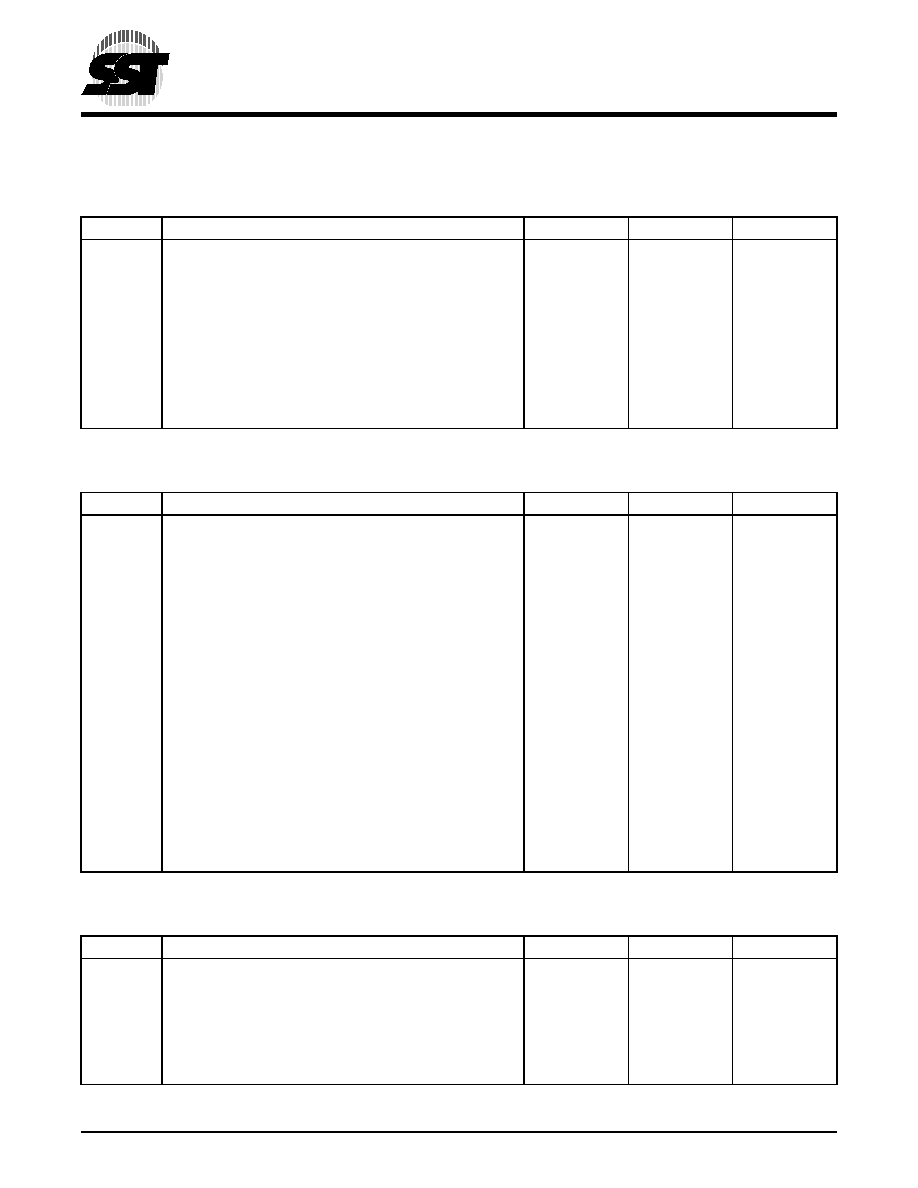

AC CHARACTERISTICS (PP MODE)

TABLE 20: READ CYCLE TIMING PARAMETERS VDD =3.0-3.6V (PP MODE)

Symbol

Parameter

Min

Max

Units

TRC

Read Cycle Time

270

ns

TRST

RST# High to Row Address Setup

1

s

TAS

R/C# Address Set-up Time

45

ns

TAH

R/C# Address Hold Time

45

ns

TAA

Address Access Time

120

ns

TOE

Output Enable Access Time

60

ns

TOLZ

OE# Low to Active Output

0

ns

TOHZ

OE# High to High-Z Output

35

ns

TOH

Output Hold from Address Change

0

ns

T20.2 504

TABLE 21: PROGRAM/ERASE CYCLE TIMING PARAMETERS VDD =3.0-3.6V (PP MODE)

Symbol

Parameter

Min

Max

Units

TRST

RST# High to Row Address Setup

1

s

TAS

R/C# Address Setup Time

50

ns

TAH

R/C# Address Hold Time

50

ns

TCWH

R/C# to Write Enable High Time

50

ns

TOES

OE# High Setup Time

20

ns

TOEH

OE# High Hold Time

20

ns

TOEP

OE# to Data# Polling Delay

40

ns

TOET

OE# to Toggle Bit Delay

40

ns

TWP

WE# Pulse Width

100

ns

TWPH

WE# Pulse Width High

100

ns

TDS

Data Setup Time

50

ns

TDH

Data Hold Time

5

ns

TIDA

Software ID Access and Exit Time

150

ns

TBP

Byte Programming Time

20

s

TSE

Sector-Erase Time

25

ms

TBE

Block-Erase Time

25

ms

TSCE

Chip-Erase Time

100

ms

T21.2 504

TABLE 22: RESET TIMING PARAMETERS, VDD =3.0-3.6V (PP MODE)

Symbol

Parameter

Min

Max

Units

TPRST

VDD stable to Reset Low

1

ms

TRSTP

RST# Pulse Width

100

ns

TRSTF

RST# Low to Output Float

48

ns

TRST1

1. There will be a reset latency of TRSTE or TRSTC if a reset procedure is performed during a Program or Erase operation.

RST# High to Row Address Setup

1

s

TRSTE

RST# Low to reset during Sector-/Block-Erase or Program

10

s

TRSTC

RST# Low to reset during Chip-Erase

50

s

T22.1 504

相关PDF资料 |

PDF描述 |

|---|---|

| 4A000MH5 | 2-Input NAND Gate |

| 4A002MH5 | 2-Input NOR Gate |

| 4A004MH5 | 4A004MH5 |

| 4A032MH5 | 4A032MH5 |

| 4A08P-505-500 | Surge Line Protection Module |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 49LV1614-90TI | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 49M-011059-FX4X10 | 制造商:Aker Technology Company Ltd 功能描述:FX4X10 Series 11.0590MHZ 30PPM 20PF SMD Crystal |

| 49M-027000-FX4X12 | 制造商:Aker Technology Company Ltd 功能描述:FX4X12 Series 27MHZ 30PPM 20PF SMD Crystal |

| 49M-10 | 制造商:Honeywell Sensing and Control 功能描述: |

| 49M1K | 功能描述:工业移动感应器和位置传感器 RESISTIVE & OPTICAL RoHS:否 制造商:Honeywell 输出类型:Analog - Current 电压额定值:12 VDC to 30 VDC 线性:+/- 0.0011 % 温度范围:- 40 C to + 85 C 总电阻: 容差: 类型:Rotary Sensor |

发布紧急采购,3分钟左右您将得到回复。