- 您现在的位置:买卖IC网 > PDF目录33810 > 48e30 (Holtek Semiconductor Inc.) 8-Bit I/O Type MCU (With EEPROM) PDF资料下载

参数资料

| 型号: | 48e30 |

| 厂商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit I/O Type MCU (With EEPROM) |

| 中文描述: | 8位I / O型微控制器(带EEPROM) |

| 文件页数: | 1/44页 |

| 文件大小: | 351K |

| 代理商: | 48E30 |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

HT48E30

8-Bit I/O Type MCU (With EEPROM)

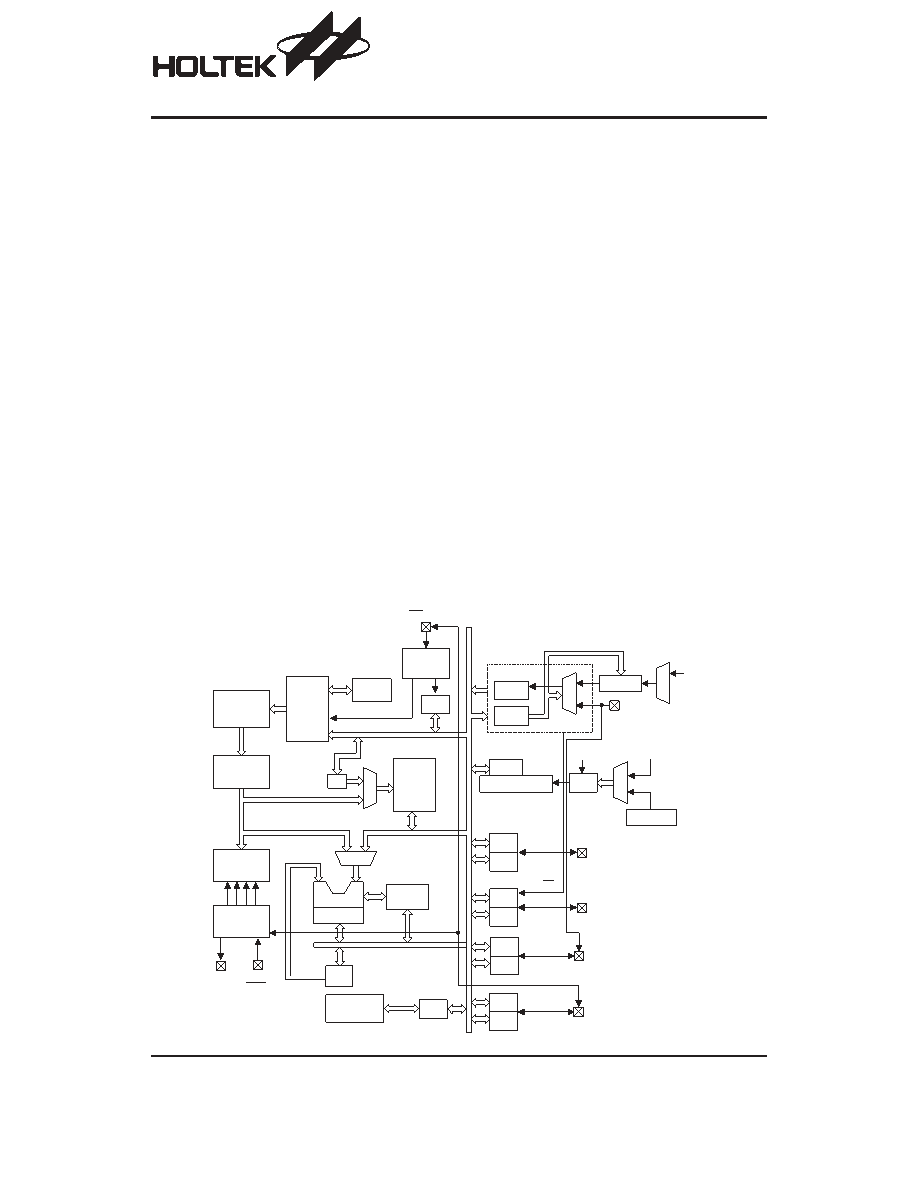

Block Diagram

Rev. 0.00

1

January 12, 2004

General Description

The HT48E30 is an 8-bit high performance, RISC archi-

tecture microcontroller device specifically designed for

multiple I/O control product applications.

The advantages of low power consumption, I/O flexibil-

ity, timer functions, oscillator options, HALT and

wake-up functions, watchdog timer, buzzer driver, as

well as low cost, enhance the versatility of these devices

to suit a wide range of application possibilities such as

industrial control, consumer products, subsystem con-

trollers, etc.

Features

Operating voltage:

fSYS=4MHz: 2.2V~5.5V

fSYS=8MHz: 3.3V~5.5V

Low voltage reset function

23 bidirectional I/O lines (max.)

1 interrupt input shared with an I/O line

8-bit programmable timer/event counter with overflow

interrupt and 8-stage prescaler

On-chip crystal and RC oscillator

Watchdog Timer

204814 program memory ROM (MTP)

1288 data memory EEPROM

968 data memory RAM

Buzzer driving pair and PFD supported

HALT function and wake-up feature reduce power

consumption

4-level subroutine nesting

Up to 0.5ms instruction cycle with 8MHz system clock

at VDD=5V

Bit manipulation instruction

14-bit table read instruction

63 powerful instructions

106 erase/write cycles EEPROM data memory

EEPROM data retention > 10 years

All instructions in one or two machine cycles

In system programming (ISP)

24/28-pin SKDIP/SOP package

I N T / P G 0

O S C 2

O S C 1

R E S

V D D

M U X

T M R / P C 0

T M R 0 C

T M R 0

V S S

P r e s c a l e r

f S Y S

P G 0

P r o g r a m

R O M

P r o g r a m

C o u n t e r

I n t e r r u p t

C i r c u i t

S T A C K

4 L e v e l s

I N T C

D A T A

M e m o r y

I n s t r u c t i o n

R e g i s t e r

M

U

X

I n s t r u c t i o n

D e c o d e r

S T A T U S

A L U

S h i f t e r

T i m i n g

G e n e r a t o r

A C C

M

U

X

M P

W D T S

W D T

W D T O S C

W D T P r e s c a l e r

M

U

X

E N / D I S

P G 1

P G 2

P G C

P G

P O R T G

P B C

P O R T B

P B 0 ~ P B 7

B Z / B Z

P B

P A C

P O R T A

P A 0 ~ P A 7

P A

P C

P O R T C

P C 0 ~ P C 5

P C C

M

U

X

f S Y S / 4

P G 0

D a t a M e m o r y

E E P R O M

E E C R

Preliminary

相关PDF资料 |

PDF描述 |

|---|---|

| 48L120D | STANDARD RECOVERY DIODES |

| 48L160D | STANDARD RECOVERY DIODES |

| 48LF120D | CAP 1500PF 50V CERAMIC MONO 5% |

| 48LF160D | STANDARD RECOVERY DIODES |

| 48LFR120D | STANDARD RECOVERY DIODES |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 48-EM | 制造商:ITW Switches 功能描述:ELECTROMECHANICAL SWITCH KIT, Kit Contents:Miniature Sealed Electro-Mechanical P |

| 48ES | 制造商:VISUAL COMMUNICATIONS COMPANY LLC 功能描述:48ES /Custom Part |

| 48ESB | 功能描述:灯 Telephone Slide Base .04A .358M ANSI#5 RoHS:否 制造商:Chicago Miniature 灯类型:Incandescent 灯座类型:Wire Terminal 灯大小:T-1 3/4 颜色: 电压:14 V 工作电流: MSCP:0.3 MSCP 寿命:40000 hr 封装:Bulk |

| 48ESB- | 功能描述:LAMP T-2 TELEPHONE SLIDE 48V RoHS:是 类别:光电元件 >> 灯 - 白炽灯,氖灯 系列:- 标准包装:100 系列:- 颜色:透明 透镜样式/尺寸:圆形,带圆顶,5mm,T-1 3/4 引线型:小型凹槽 MSCP(平均球面烛光):0.3 额定电压:60V 其它名称:913.4005913.4005-ND |

| 48ESB | 制造商:PRIVATE LABEL 功能描述:Incandescent Filament Lamp, Voltage Rating:48V, Bulb Size:T-2, Lamp Ba Type:Slide |

发布紧急采购,3分钟左右您将得到回复。