- 您现在的位置:买卖IC网 > PDF目录156551 > 37C67X (SMSC Corporation) ENHANCED SUPER I/O CONTROLLER WITH FAST IR PDF资料下载

参数资料

| 型号: | 37C67X |

| 厂商: | SMSC Corporation |

| 英文描述: | ENHANCED SUPER I/O CONTROLLER WITH FAST IR |

| 中文描述: | 增强的超级I / O控制器,快速红外线 |

| 文件页数: | 122/194页 |

| 文件大小: | 546K |

| 代理商: | 37C67X |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页当前第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页

33

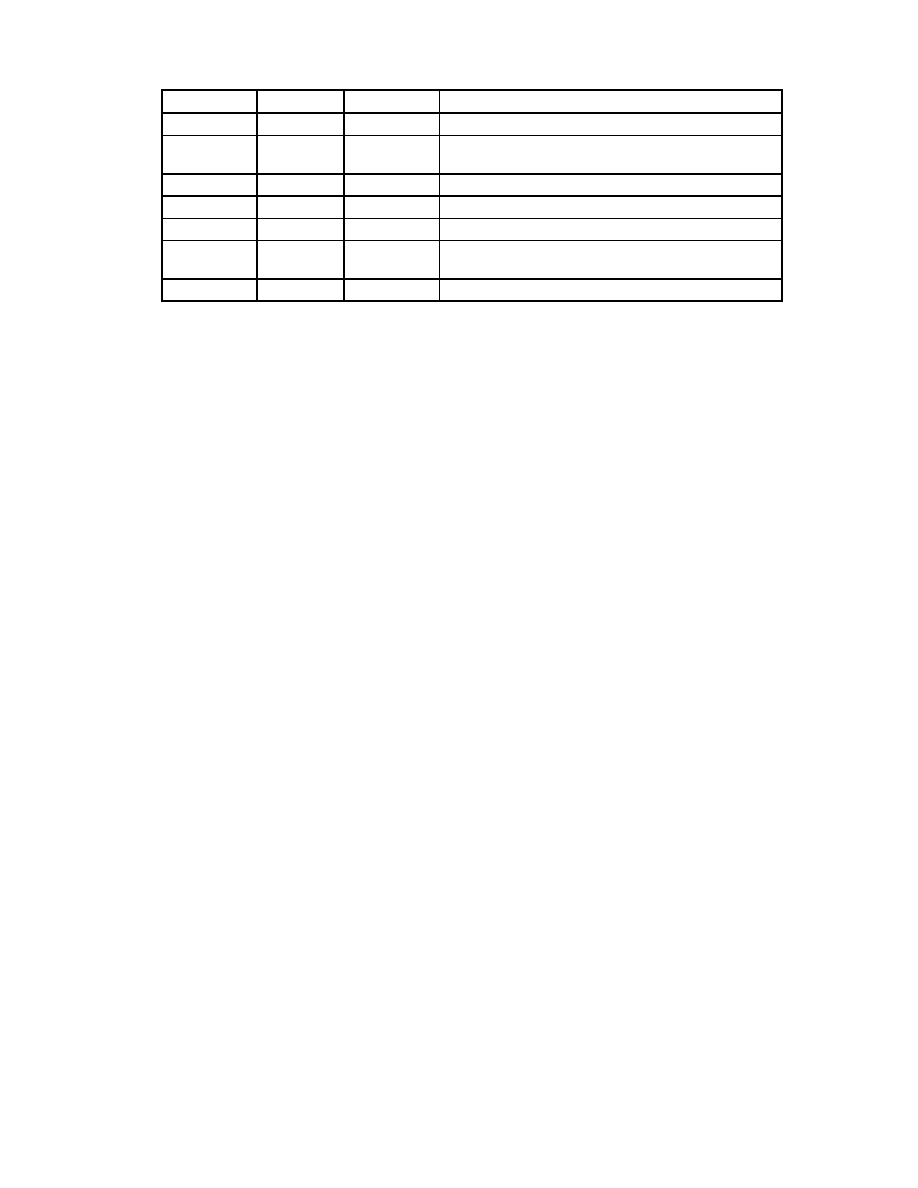

Table 18- Status Register 3

BIT NO.

SYMBOL

NAME

DESCRIPTION

7

Unused. This bit is always "0".

6

WP

Write

Protected

Indicates the status of the WP pin.

5

Unused. This bit is always "1".

4

T0

Track 0

Indicates the status of the TRK0 pin.

3

Unused. This bit is always "1".

2

HD

Head

Address

Indicates the status of the HDSEL pin.

1,0

DS1,0

Drive Select

Indicates the status of the DS1, DS0 pins.

RESET

There are three sources of system reset on the

FDC: the RESET pin of the FDC, a reset

generated via a bit in the DOR, and a reset

generated via a bit in the DSR. At power on, a

Power On Reset initializes the FDC. All resets

take the FDC out of the power down state.

All operations are terminated upon a RESET,

and the FDC enters an idle state. A reset while

a disk write is in progress will corrupt the data

and CRC.

On exiting the reset state, various internal

registers are cleared, including the Configure

command information, and the FDC waits for a

new command.

Drive polling will start unless

disabled by a new Configure command.

RESET Pin (Hardware Reset)

The RESET pin is a global reset and clears all

registers except those programmed by the

Specify command.

The DOR reset bit is

enabled and must be cleared by the host to exit

the reset state.

DOR Reset vs. DSR Reset (Software Reset)

These two resets are functionally the same.

Both will reset the FDC core, which affects drive

status information and the FIFO circuits. The

DSR reset clears itself automatically while the

DOR reset requires the host to manually clear it.

DOR reset has precedence over the DSR reset.

The DOR reset is set automatically upon a pin

reset. The user must manually clear this reset

bit in the DOR to exit the reset state.

MODES OF OPERATION

The FDC has three modes of operation, PC/AT

mode, PS/2 mode and Model 30 mode. These

are determined by the state of the IDENT and

MFM bits 6 and 5 respectively of CRxx.

PC/AT mode - (IDENT high, MFM a "don't

care")

The PC/AT register set is enabled, the DMA

enable bit of the DOR becomes valid (FINTR

and DRQ can be hi Z), and TC and DENSEL

become active high signals.

相关PDF资料 |

PDF描述 |

|---|---|

| 37C957FR | ULTRA I/O CONTROLLER FOR PORTABLE APPLICATIONS |

| 37FMA1-ABW31N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 0.2A, 24VDC, PANEL MOUNT-THREADED |

| 37FML1-BEW31N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 0.2A, 24VDC, PANEL MOUNT-THREADED |

| 37FML2-ACW21N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 1A, 24VDC, PANEL MOUNT-THREADED |

| 37FMA1-AAW11N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 0.2A, 24VDC, PANEL MOUNT-THREADED |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 37C-6BH-5-5 | 制造商:Birtcher Products 功能描述: |

| 37C72U-185 | 制造商:White-Rodgers 功能描述: |

| 37C73U-170 | 制造商:White-Rodgers 功能描述: |

| 37C73U-171 | 制造商:White-Rodgers 功能描述: |

| 37C922BQFP | 制造商:SMSC 功能描述: |

发布紧急采购,3分钟左右您将得到回复。