参数资料

| 型号: | XC4VFX12-10SFG363C |

| 厂商: | Xilinx Inc |

| 文件页数: | 26/58页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX-4 FX 12K 363FCBGA |

| 标准包装: | 90 |

| 系列: | Virtex®-4 FX |

| LAB/CLB数: | 1368 |

| 逻辑元件/单元数: | 12312 |

| RAM 位总计: | 663552 |

| 输入/输出数: | 240 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 363-FBGA,FCBGA |

| 供应商设备封装: | 363-FCBGA(17x17) |

| 配用: | HW-V4-ML403-UNI-G-ND - EVALUATION PLATFORM VIRTEX-4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

Virtex-4 FPGA Data Sheet: DC and Switching Characteristics

DS302 (v3.7) September 9, 2009

Product Specification

32

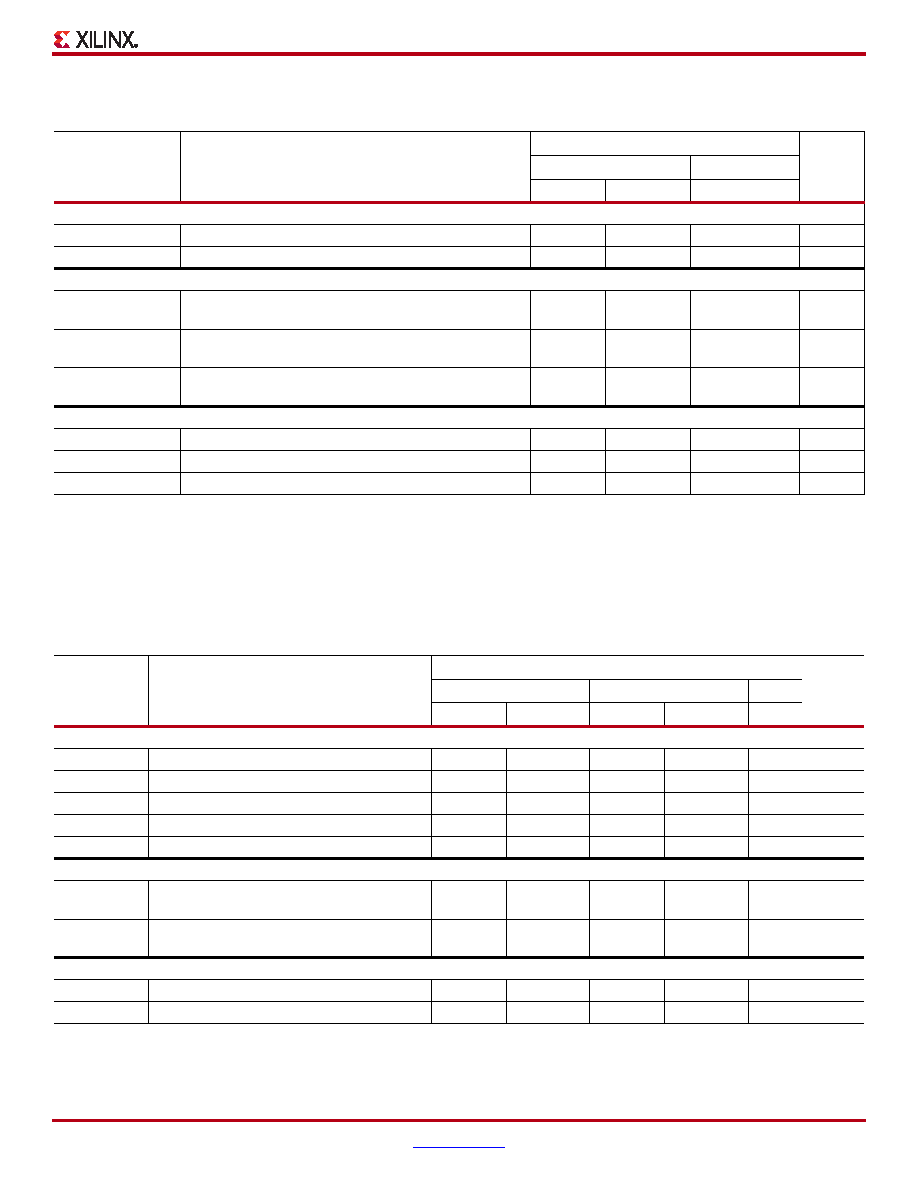

CLB Distributed RAM Switching Characteristics (SLICEM Only)

)

CLB Shift Register Switching Characteristics (SLICEM Only)

)

Table 38: CLB Distributed RAM Switching Characteristics

Symbol

Description

Speed Grade

Units

-12

-11

-10

XC4VFX(2)

XC4VLX/SX

ALL DEVICES

Sequential Delays

TSHCKO

Clock CLK to X outputs (WE active)(3)

1.61

1.58

1.77

2.08

ns, Max

TSHCKOF5

Clock CLK to F5 output (WE active)

1.53

1.50

1.69

1.98

ns, Max

Setup and Hold Times Before/After Clock CLK

TDS / TDH

BX/BY data inputs (DI)

1.26

–0.90

1.23

–0.88

1.46

–0.88

1.80

–0.88

ns, Min

TAS / TAH

F/G address inputs

0.88

–0.37

0.86

–0.37

0.97

–0.34

1.13

–0.29

ns, Min

TWS / TWH

WE input (SR)

1.10

–0.48

1.08

–0.47

1.21

–0.47

1.42

–0.47

ns, Min

Clock CLK

TWPH

Minimum Pulse Width, High

0.53

0.52

0.59

0.69

ns, Min

TWPL

Minimum Pulse Width, Low

0.55

0.54

0.60

0.70

ns, Min

TWC

Minimum clock period to meet address write cycle time

0.76

0.74

0.84

0.98

ns, Min

Notes:

1.

A Zero “0” Hold Time listing indicates no hold time or a negative hold time. Negative values cannot be guaranteed “best-case,” but if a “0” is listed,

there is no positive hold time.

2.

The values in this column apply to all XC4VFX -12 parts except XC4VFX12 -12. For XC4VFX12 -12 values, use the values in the adjacent

XC4VLX/SX -12 column.

3.

TSHCKO also represents the CLK to XMUX output. Refer to TRCE report for the CLK to XMUX path.

Table 39: CLB Shift Register Switching Characteristics

Symbol

Description

Speed Grade

Units

-12

-11

-10

XC4VFX(2)

XC4VLX/SX

XC4VFX(3)

XC4VLX/SX

ALL

Sequential Delays

TREG

Clock CLK to X/Y outputs

2.12

2.08

2.19

2.57

ns, Max

TREGXB

Clock CLK to XB output via MC15 LUT output

1.83

1.73

1.90

1.84

2.16

ns, Max

TREGYB

Clock CLK to YB output via MC15 LUT output

1.84

1.74

1.92

1.85

2.17

ns, Max

TCKSH

Clock CLK to Shiftout

1.70

1.60

1.76

1.70

1.99

ns, Max

TREGF5

Clock CLK to F5 output

2.05

2.01

2.11

2.47

ns, Max

Setup and Hold Times Before/After Clock CLK

TWS / TWH

WE input (SR)

0.87

–0.76

0.85

–0.76

0.96

–0.70

0.96

–0.70

1.12

–0.62

ns, Min

TDS / TDH

BX/BY data inputs (DI)

1.28

–1.12

1.25

–1.11

1.45

–1.11

1.45

–1.11

1.75

–1.11

ns, Min

Clock CLK

TWPH

Minimum Pulse Width, High

0.53

0.52

0.59

0.69

ns, Min

TWPL

Minimum Pulse Width, Low

0.55

0.54

0.60

0.70

ns, Min

Notes:

1.

A Zero “0” Hold Time listing indicates no hold time or a negative hold time. Negative values cannot be guaranteed “best-case,” but if a “0” is listed,

there is no positive hold time.

2.

The values in this column apply to all XC4VFX -12 parts except XC4VFX12 -12. For XC4VFX12 -12 values, use the values in the adjacent

XC4VLX/SX -12 column.

3.

The values in this column apply to all XC4VFX -11 parts.

相关PDF资料 |

PDF描述 |

|---|---|

| 23K640-E/ST | IC SRAM 64KBIT 20MHZ 8TSSOP |

| SST25VF020B-80-4I-SAE-T | IC FLASH SER 2MB 80MHZ SPI 8SOIC |

| XC2S400E-6FGG456C | IC SPARTAN-IIE FPGA 400K 456FBGA |

| XA6SLX100-2FGG484I | IC FPGA SPARTAN 6 484FGGBGA |

| 25LC640T-E/SN | IC EEPROM 64KBIT 2MHZ 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4VFX12-10SFG363I | 功能描述:IC FPGA VIRTEX-4 FX 12K 363FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 FX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VFX12-11FF668C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 12312 CELLS 90NM 1.2V 668FCBGA - Trays |

| XC4VFX12-11FF668I | 功能描述:IC FPGA VIRTEX-4FX 668FFBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 FX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VFX12-11FFG668C | 功能描述:IC FPGA VIRTEX-4 FX 12K 668FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 FX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VFX12-11FFG668I | 功能描述:IC FPGA VIRTEX-4 FX 12K 668FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 FX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

发布紧急采购,3分钟左右您将得到回复。