- 您现在的位置:买卖IC网 > PDF目录98215 > TFP6424PAP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF资料下载

参数资料

| 型号: | TFP6424PAP |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, 0.50 MM PITCH, THERMALLY ENHANCED, POWER, PLASTIC, TQFP-64 |

| 文件页数: | 27/65页 |

| 文件大小: | 813K |

| 代理商: | TFP6424PAP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页

TFP6422, TFP6424

PanelBus

DIGITAL TRANSMITTER/VIDEO ENCODER COMBO

SLDS118 – MARCH 2000

33

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

register description

The default register settings are indicated with (*). If two defaults are indicated, the state of INT0 / CBARE at

reset will determine which default is used.

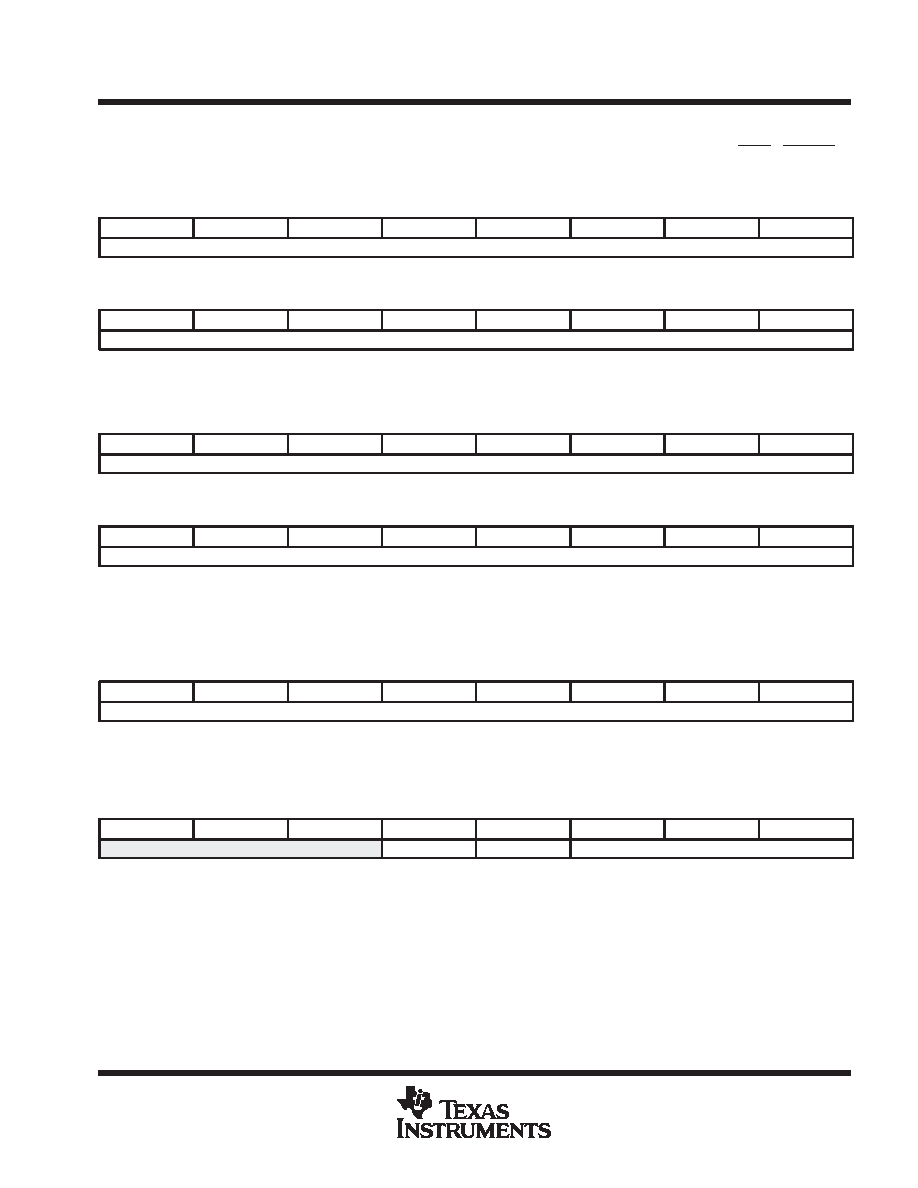

VEN_ID

Subaddress = 00

Read Only

Default = 0x4C

7

6

5

4

3

2

1

0

VEN_ID[7:0]

Subaddress = 01

Read Only

Default = 0x01

7

6

5

4

3

2

1

0

VEN_ID[15:8]

This read-only register contains the 16–bit Texas Instruments vendor ID for the TFP6422/6424. VEN_ID[15:0]

is hardwired to 0x014C.

DEV_ID

Subaddress = 02

Read Only

Default = 0x22/23

7

6

5

4

3

2

1

0

DEV_ID[7:0]

Subaddress = 03

Read Only

Default = 0x64

7

6

5

4

3

2

1

0

DEV_ID[15:8]

This read-only register contains the 16-bit device ID for the TFP6422 and TFP6424. The revision ID will identify

different revisions of the device. For TFP6422, DEV_ID[15:0] is hardwired to 0x6422. For TFP6424,

DEV_ID[15:0] is hardwired to 0x6424.

REV_ID

Subaddress = 03

Read Only

Default = 0x01

7

6

5

4

3

2

1

0

REV_ID[7:0]

This read-only register contains the revision ID for the TFP6422 and TFP6424. The revision ID will identify

different revisions of the device. REV_ID[7:0] is hardwired to 0x01.

STATUS

Subaddress = 05

Read Only

7

6

5

4

3

2

1

0

CCE

CCO

FSQ[2:0]

CCE

Closed caption status for even field. This bit is set immediately after the data in registers LINE21_E0 and

LINE21_E1 have been encoded to closed caption. This bit is reset when both of these registers are written.

CCO

Closed caption status for odd field. This bit is set immediately after the data in registers LINE21_O0 and

LINE21_O1 have been encoded to closed caption. This bit is reset when both of these registers are written.

FSQ[2:0] Field sequence ID. For PAL, all three FSQ[2:0] are used whereas for NTSC only FSQ[1:0] is meaningful.

Furthermore, FSQ[0] represents ODD field when it is 0 and EVEN field when it is 1.

PRODUCT

PREVIEW

相关PDF资料 |

PDF描述 |

|---|---|

| TFP9431CPAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TG355ENK-7916 | 8.15 MHz, LOW PASS FILTER |

| TH355BDI-4957 | 4.43 MHz, BAND PASS FILTER |

| TH355LDK-7915 | 8.15 MHz, LOW PASS FILTER |

| TH355LNK-4550 | 10 MHz, LOW PASS FILTER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TFP70N06 | 制造商:TAK_CHEONG 制造商全称:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 70A, 60V, 0.014Ω |

| TFP730 | 制造商:TAK_CHEONG 制造商全称:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 5.5A, 400V, 0.95Ω |

| TFP740 | 制造商:TAK_CHEONG 制造商全称:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 10A, 400V, 0.55Ω |

| TFP7433PZP | 制造商:Texas Instruments 功能描述: |

| TFP7445PZP-6 | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。