- 您现在的位置:买卖IC网 > PDF目录16462 > EVAL-AD1940AZ (Analog Devices Inc)BOARD EVAL AD1940 SIGMADSP PDF资料下载

参数资料

| 型号: | EVAL-AD1940AZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 25/36页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL AD1940 SIGMADSP |

| 标准包装: | 1 |

| 系列: | SigmaDSP® |

| 主要目的: | 音频,音频处理 |

| 嵌入式: | 是,DSP |

| 已用 IC / 零件: | AD1940 |

| 主要属性: | 单芯片多通道 28/56 位音频 DSP |

| 次要属性: | 均衡,交叉,低音增强,多频带动态处理,延迟等 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD1940/AD1941

Rev. B | Page 31 of 3

6

BCLK Polarity (Bit 3)

This bit controls on which edge of the bit clock the input data

changes, and on which edge it is clocked. Data changes on the

falling edge of BCLK_IN when this bit is set to 0, and on the

rising edge when this bit is set at 1.

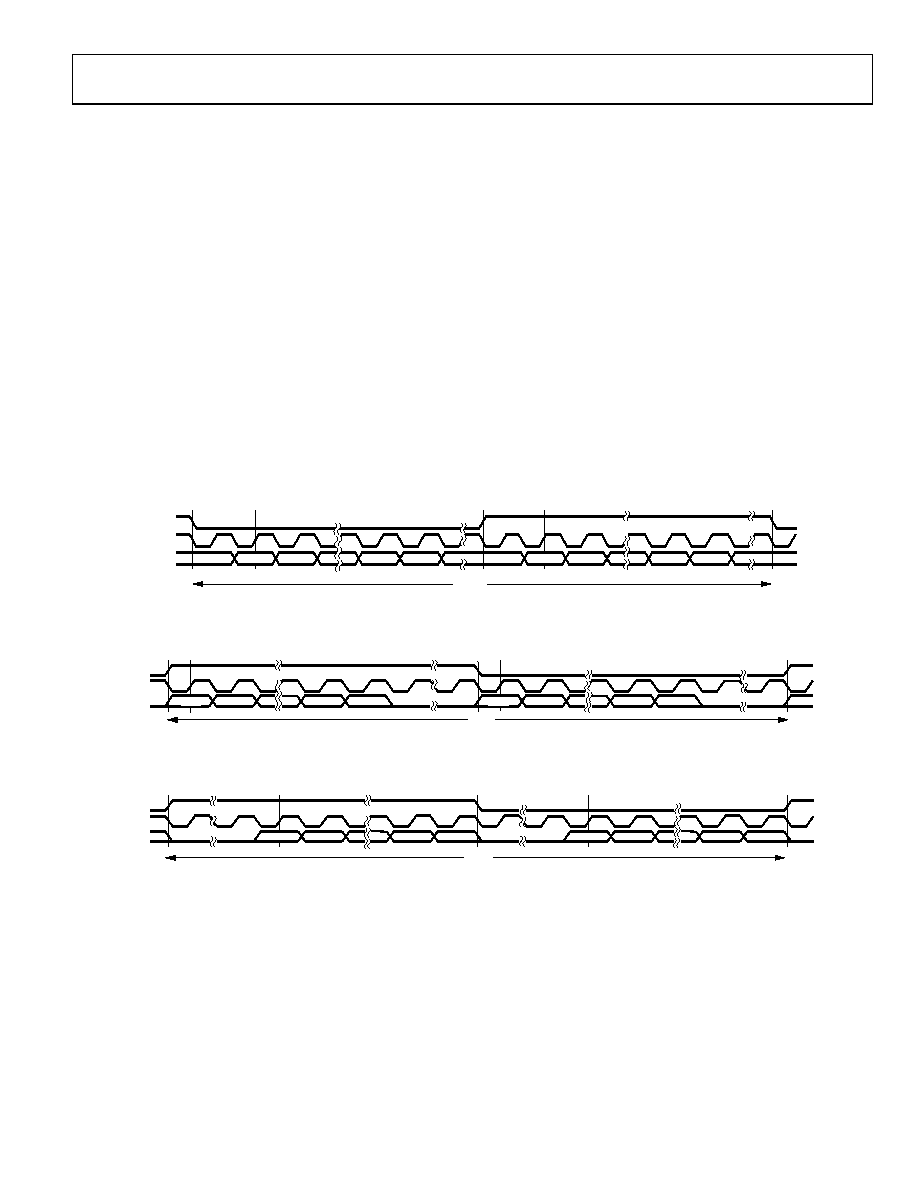

Serial Input Mode (Bits 2:0)

These two bits control the data format that the input port

expects to receive. Bits 3 and 4 of this control register override

the settings in Bits 2:0, so all four bits must be changed together

for proper operation in some modes. The clock diagrams for

these modes are shown in Figure 23, Figure 24, and Figure 25.

Note that for left-justified and right-justified modes the LRCLK

polarity is high, then low, which is opposite from the default

setting of Bit 4.

When these bits are set to accept a TDM input, the AD1940/

AD1941’s data starts after the edge defined by Bit 4. Figure 26

shows an 8-channel TDM stream with a high-to-low triggered

LRCLK and data changing on the falling edge of the BCLK. The

AD1940/AD1941 expects the MSB of each data slot delayed by

one BCLK from the beginning of the slot, just like in the stereo

I2S format. In 8-channel TDM mode, Channels 0 to 3 are in the

first half of the frame, and Channels 4 to 7 are in the second

half. When in 16-channel TDM mode, the first half-frame holds

Channels 0 to 7, and the second half-frame holds Channels 8 to

15. Figure 26 shows just one of the formats in which the

AD1940/AD1941 can operate in TDM mode. Please refer to the

Serial Data Input/Output Ports section for a more complete

description of the modes of operation. Figure 27 shows an

example of a TDM stream running with a pulse word clock,

which would be used to interface to ADI codecs in their

auxiliary mode. To work in this mode on either the input or

output serial ports, the AD1940/AD1941 should be set to frame

beginning on the rising edge of LRCLK, data changing on the

falling edge of BCLK, and MSB position delayed from the start

of the word clock by one BCLK.

Table 37 explains the clock settings for each of these formats.

LRCLK

BCLK

SDATA

MSB

LEFT CHANNEL

LSB

MSB

RIGHT CHANNEL

LSB

1 /FS

04607-0-023

Figure 23. I2S Mode—16 to 24 Bits per Channel

LRCLK

BCLK

SDATA

LEFT CHANNEL

MSB

LSB

MSB

RIGHT CHANNEL

LSB

1 /FS

04607-0-024

Figure 24. Left-Justified Mode—16 to 24 Bits per Channel

LRCLK

BCLK

SDATA

LEFT CHANNEL

MSB

LSB

MSB

RIGHT CHANNEL

LSB

1 /FS

04607-0-025

Figure 25. Right-Justified Mode—16 to 24 Bits per Channel

相关PDF资料 |

PDF描述 |

|---|---|

| 6278128-6 | MT-RJ/MT-RJ 6M1 C/A |

| 1-1906054-0 | CA 2MM OFNR 62.5/125,LC SEC GRE |

| M3DRK-1006J | IDC CABLE - MKR10K/MC10G/MPR10K |

| VE-20J-EX | CONVERTER MOD DC/DC 36V 75W |

| RNF-100-1-GY-SP | HEAT SHRINK TUBING |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD1940EB | 制造商:Analog Devices 功能描述:DEV TOOLS, SIGMADSPTM MULTICH 28BIT AUD PROCESSOR - Bulk |

| EVAL-AD1940MINIB | 制造商:Analog Devices 功能描述:SIGMADSP EVAL BD - Bulk 制造商:Rochester Electronics LLC 功能描述: |

| EVAL-AD1940MINIBZ | 功能描述:BOARD EVAL AD1940 MINI SIGMADSP RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:SigmaDSP® 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| EVAL-AD1941EB | 制造商:Analog Devices 功能描述:EVAL BD SIGMADSPMULTICHANAUDIO PROCESSOR - Bulk |

| EVAL-AD1953EB | 制造商:Analog Devices 功能描述:EVAL BRD FOR 3 CH 24 BIT SIG-PROCESS DAC - Bulk 制造商:Analog Devices 功能描述:EVALUATION KIT ((NS)) |

发布紧急采购,3分钟左右您将得到回复。