- 您现在的位置:买卖IC网 > PDF目录25515 > 952601YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 952601YGLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-56 |

| 文件页数: | 10/25页 |

| 文件大小: | 227K |

| 代理商: | 952601YGLFT |

IDTTM

Progammable Timing Control HubTM for Next Gen P4TM Processor

701J—01/25/10

ICS952601

Programmable Timing Control HubTM for Next Gen P4TM Processor

18

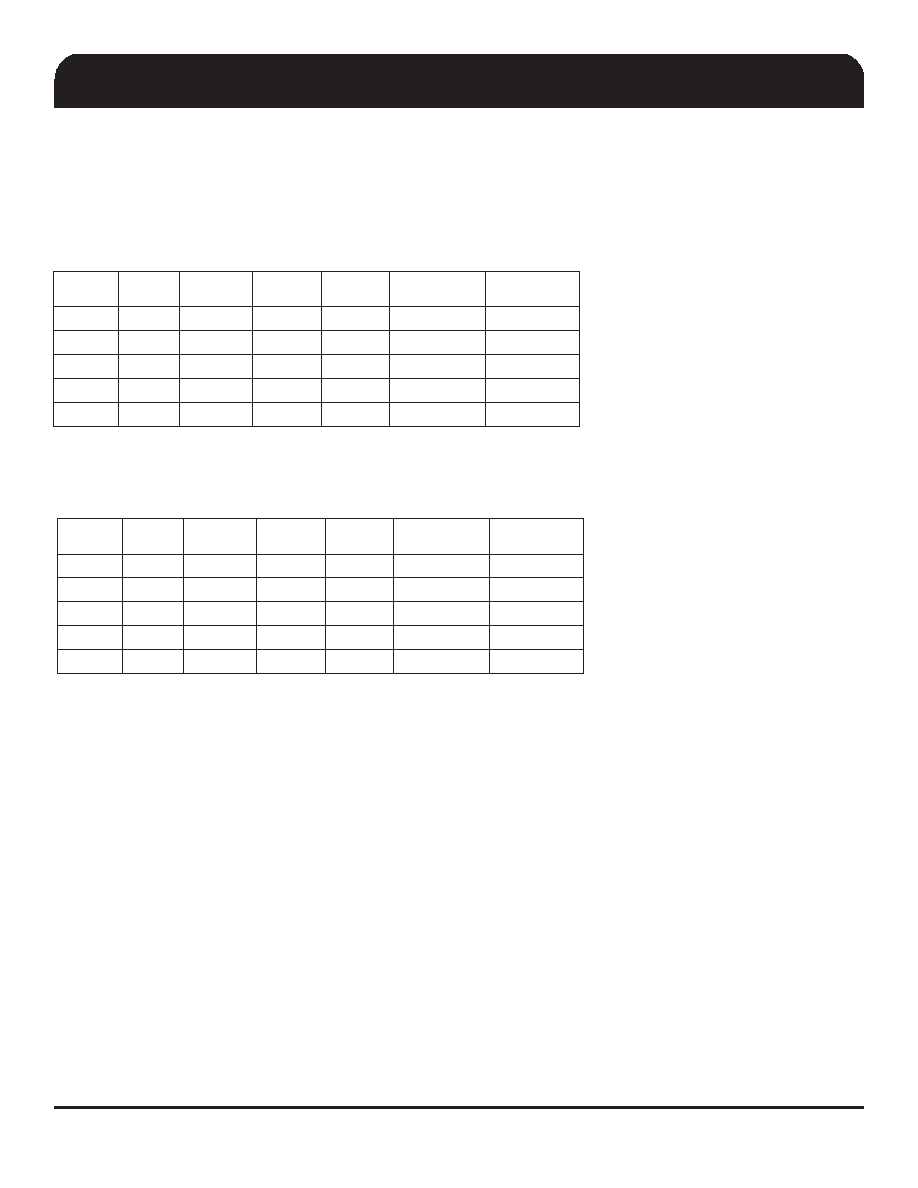

To minimize power consumption, CPU[2:0] clock outputs are individually configurable through SMBus to be driven or

tristated during PwrDwn# and CPU_Stop# mode and the SRC clock is configurable to be driven or tristated during

PCI_Stop# and PwrDwn# mode. Each differential clock (SRC, CPU[2:0]) output can be disabled by setting the

corresponding output's register OE bit to "0" (disable). Disabled outputs are to be tristated regardless of "CPU_Stop",

"SRC_Stop" and "PwrDwn" register bit settings.

l

a

n

g

i

S#

D

P

n

i

Pn

i

P

#

p

o

t

S

_

U

P

C

p

o

t

S

_

U

P

C

t

i

B

e

t

a

t

s

i

r

T

n

w

d

r

w

P

t

i

B

e

t

a

t

s

i

r

T

e

l

b

a

p

o

t

S

-

n

o

N

s

t

u

p

t

u

O

e

l

b

a

p

o

t

S

s

t

u

p

t

u

O

}

0

:

2

[

U

P

C1

1

X

g

n

i

n

u

Rg

n

i

n

u

R

}

0

:

2

[

U

P

C1

0

Xg

n

i

n

u

R6

x

f

e

r

I

@

n

e

v

i

r

D

}

0

:

2

[

U

P

C1

0

1

X

g

n

i

n

u

Re

t

a

t

s

i

r

T

}

0

:

2

[

U

P

C0

X

0

2

x

f

e

r

I

@

n

e

v

i

r

D2

x

f

e

r

I

@

n

e

v

i

r

D

}

0

:

2

[

U

P

C0

X

1

e

t

a

t

s

i

r

Te

t

a

t

s

i

r

T

Notes:

1. Each output has four corresponding control register bits, OE, PwrDwn, CPU_Stop and "Free Running"

2. Iref x 6 and Iref x 2 is the output current in the corresponding mode

3. See Control Registers section for bit address

l

a

n

g

i

S#

D

P

n

i

Pn

i

P

#

p

o

t

S

_

I

C

P

p

o

t

S

_

I

C

P

t

i

B

e

t

a

t

s

i

r

T

n

w

d

r

w

P

t

i

B

e

t

a

t

s

i

r

T

e

l

b

a

p

o

t

S

-

n

o

N

t

u

p

t

u

O

e

l

b

a

p

o

t

S

t

u

p

t

u

O

C

R

S1

1

X

g

n

i

n

u

Rg

n

i

n

u

R

C

R

S1

0

Xg

n

i

n

u

R6

x

f

e

r

I

@

n

e

v

i

r

D

C

R

S1

0

1

X

g

n

i

n

u

Re

t

a

t

s

i

r

T

C

R

S0

X

0

2

x

f

e

r

I

@

n

e

v

i

r

D2

x

f

e

r

I

@

n

e

v

i

r

D

C

R

S0

X

1

e

t

a

t

s

i

r

Te

t

a

t

s

i

r

T

Notes:

1. SRC output has four corresponding control register bits, OE, PwrDwn, SRC_Stop and "Free Running"

2. Iref x 6 and Iref x 2 is the output current in the corresponding mode

3. See Control Registers section for bit address

Differential Clock Tristate

相关PDF资料 |

PDF描述 |

|---|---|

| 952601YFLFT | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 952703BF | 217.9 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 952801CFLFT | 293.34 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 952807 | MODULAR TERMINAL BLOCK |

| 9528090000 | 10 A, MODULAR TERMINAL BLOCK, 1 DECK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 952606PFLF | 制造商:Integrated Device Technology Inc 功能描述:Programmable PLL Clock Synthesizer Dual 48-Pin SSOP Tube |

| 9526-1000-60 | 制造商:Belden Inc 功能描述:Shielded Paired Cable Number of Conducto |

| 952618BFLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 952618BFLF GENERAL PURPOSE SEMICONDUCTORS - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:IDT 952618BFLF General Purpose Semiconductors |

| 952620CFLF | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

| 952620CFLFT | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

发布紧急采购,3分钟左右您将得到回复。