- 您现在的位置:买卖IC网 > PDF目录25514 > 951412AFLF (INTEGRATED DEVICE TECHNOLOGY INC) 220 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 951412AFLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 220 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 0.300 INCH, 0.025 INCH PITCH, GREEN, MO-118, SSOP-56 |

| 文件页数: | 25/25页 |

| 文件大小: | 246K |

| 代理商: | 951412AFLF |

9

ICS951412

0883L—04/26/06

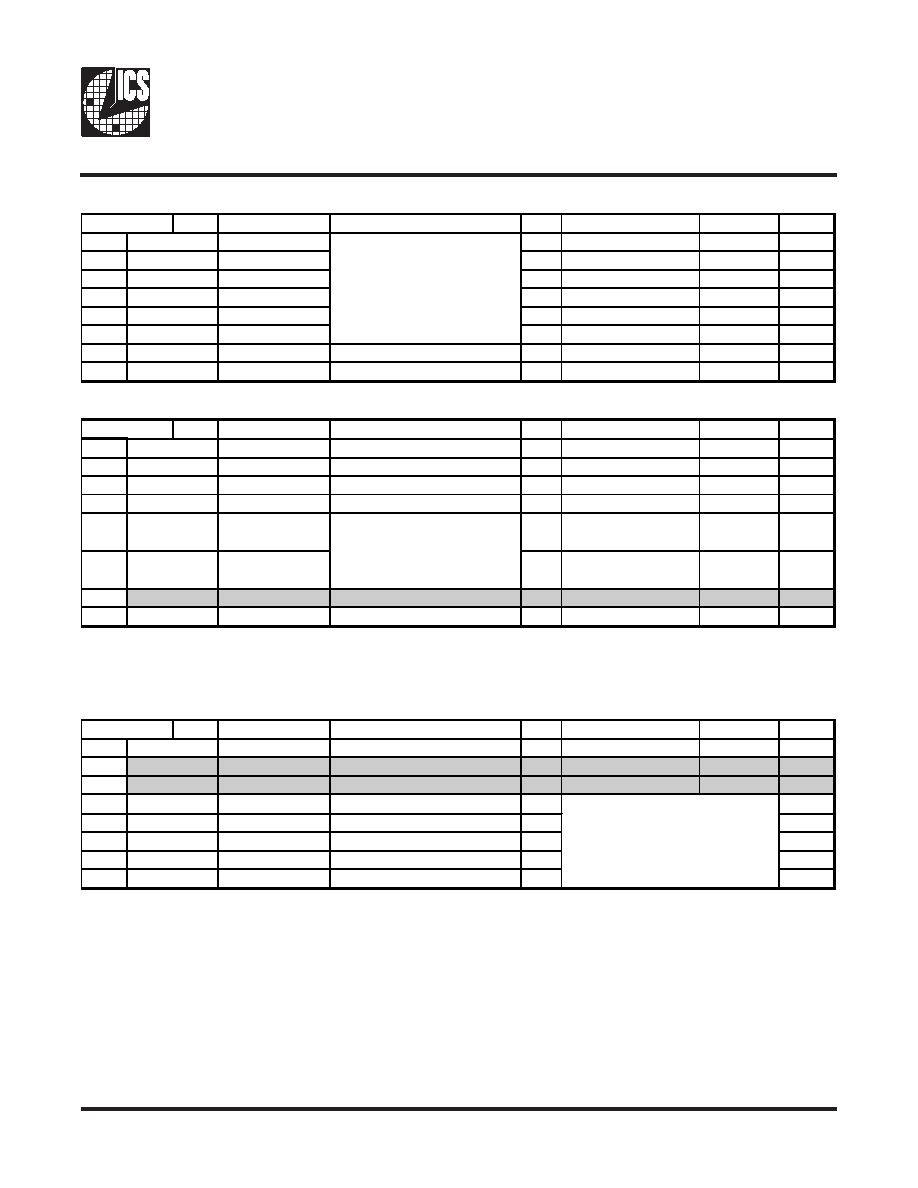

SMBus Table: SRCCLK(7:3,0), CLKREQA# Output Control Register

Pin #

Name

Control Function

Type0

1

PWD

Bit 7

SRCCLK7

RW

Disable

Enable

1

Bit 6

SRCCLK6

RW

Disable

Enable

1

Bit 5

SRCCLK5

RW

Disable

Enable

1

Bit 4

SRCCLK4

RW

Disable

Enable

1

Bit 3

SRCCLK3

RW

Disable

Enable

1

Bit 2

SRCCLK0

RW

Disable

Enable

1

Bit 1

REQASRC3

CLKREQA# Controls SRC3

RW

Does not control

Controls

0

Bit 0

REQASRC0

CLKREQA# Controls SRC0

RW

Does not control

Controls

0

SMBus Table: SRCCLK(3,0), ATIGCLK Output Control Register

Pin #

Name

Control Function

Type

0

1

PWD

Bit 7

REQASRC7

CLKREQA# Controls SRC7

RW

Does not control

Controls

0

Bit 6

REQASRC6

CLKREQA# Controls SRC6

RW

Does not control

Controls

0

Bit 5

REQASRC5

CLKREQA# Controls SRC5

RW

Does not control

Controls

0

Bit 4

REQASRC4

CLKREQA# Controls SRC4

RW

Does not control

Controls

0

Bit 3

ATIGCLK1

RW

Disabled

Enabled

1

Bit 2

ATIGCLK0

RW

Disabled

Enabled

1

Bit 1

Reserved

RW

Reserved

0

Bit 0

USB_48Str

48MHz Strength Control

RW

1X

2X

0

Note: Do NOT simultaneously select CLKREQA# and CLKREQB# to control an SRC output.

Behavior of the device is undefined under these conditions.

SMBus Table: Output Drive and ATIG Frequency Control Register

Pin #

Name

Control Function

Type0

1

PWD

Bit 7

REF2Str

REF2 Strength Control

RW

1X

2X

0

Bit 6

Reserved

RW

Reserved

0

Bit 5

Reserved

RW

Reserved

0

Bit 4

SRC SSEN

SRC Spread Enable

RW

0

Bit 3

SRCFS3

Freq Select Bit 3

RW

0

Bit 2

SRCFS2

Freq Select Bit 2

RW

0

Bit 1

SRCFS1

Freq Select Bit 1

RW

0

Bit 0

SRCFS0

Freq Select Bit 0

RW

0

-

See Table 2:

SRC Frequency Selection

Byte 5

52

-

Output Enable

These outputs cannot be

controlled by CLKREQ# pins.

30,29

-

4

16,17

18,19

22,23

27,28

24,25

34,33

Byte 4

12,13

Byte 3

12,13

Master Output control.

Enables or disables output,

regardless of CLKREQ#

inputs.

16,17

18,19

22,23

24,25

34,33

相关PDF资料 |

PDF描述 |

|---|---|

| 951412AGLF | 220 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 951413CGLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 951413CFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 951413CFLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 951416AGLF | 220 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 951412AFLFT | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 951412AGLF | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin TSSOP Tube |

| 951412AGLFT | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin TSSOP T/R |

| 951412BFLF | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin SSOP Tube |

| 951412BFLFT | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin SSOP T/R |

发布紧急采购,3分钟左右您将得到回复。